Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

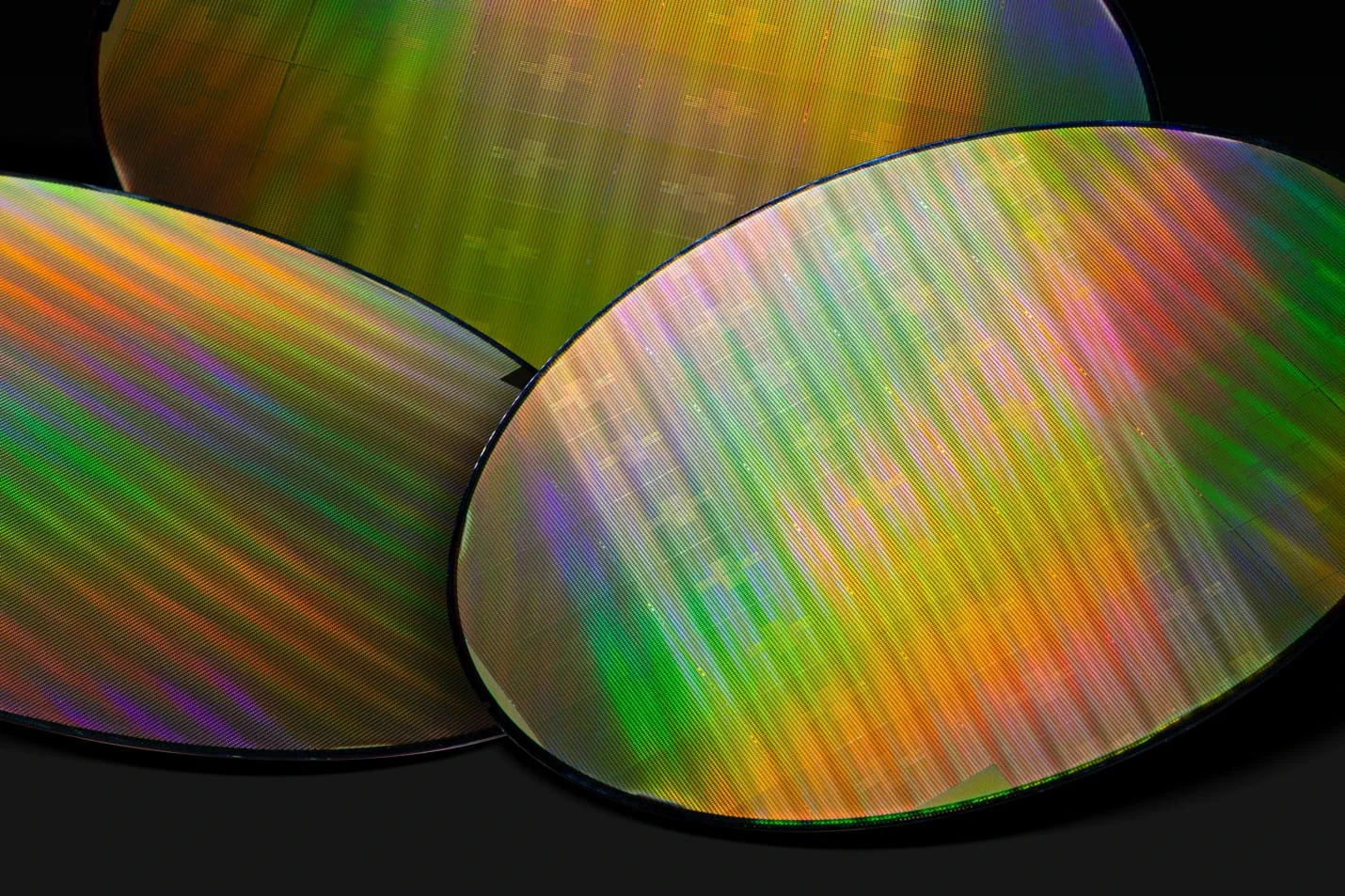

WAFER – TẤM GƯƠNG PHẢN CHIẾU CẢ THẾ GIỚI CHIP

Khi nhắc đến vi xử lý, bạn có thể tưởng tượng đến một con

chip nhỏ xíu nằm gọn trong lòng bàn tay. Nhưng ít ai biết rằng, hành trình của

con chip ấy lại bắt đầu từ một tấm wafer hình tròn, mỏng như tờ giấy,

trông như một tấm gương silicon.

Wafer là nơi chứa đựng toàn bộ sự sống của con chip – nơi

hàng tỷ transistor được sinh ra cùng lúc, với độ chính xác ở cấp độ nguyên tử.

1.

Wafer là gì?

Wafer là một tấm đĩa silicon tinh khiết có hình tròn,

đường kính tiêu chuẩn trong ngành là 200 mm (8 inch) hoặc 300 mm (12

inch). Độ dày wafer thường dưới 1 mm – mỏng đến mức có thể bị uốn cong nhẹ.

Trên mỗi wafer, có thể chế tạo hàng trăm đến hàng ngàn vi

mạch (die) cùng lúc bằng những quy trình chính xác và tự động hoá cực cao.

Tưởng tượng wafer giống như một "cánh đồng silicon", nơi các

"hạt giống thiết kế" được gieo trồng và phát triển thành thế hệ chip

tiếp theo.

2.

Wafer được tạo ra như thế nào?

Quy trình sản xuất wafer bắt đầu từ silicon tinh khiết cấp

điện tử (electronic-grade silicon) – đạt độ tinh khiết lên đến 99.9999999%

(9N). Sau đó:

- Tạo

tinh thể silicon đơn (Single-Crystal Silicon)

Bằng phương pháp Czochralski (CZ), một hạt mồi nhỏ được đưa vào chảy trong nồi silicon nóng chảy và được kéo lên chậm rãi, tạo thành một Ingot – thanh silicon đơn tinh thể, dài khoảng 1–2 mét. - Cắt

lát (Slicing)

Ingot được cắt ra thành từng lát cực mỏng (~775 μm) bằng dao cưa kim cương hoặc cưa dây (wire saw). Các lát này chính là wafer thô (raw wafer). - Mài

phẳng & đánh bóng (Lapping & Polishing)

Wafer được xử lý để đạt độ phẳng cực cao, độ nhám bề mặt chỉ còn vài nanomet – cần thiết để in mạch bằng ánh sáng với độ chính xác quang học. - Tẩy

rửa & kiểm tra chất lượng

Cuối cùng, wafer được làm sạch, khử ion, kiểm tra độ bền, độ phẳng, cấu trúc tinh thể, trước khi đưa vào các nhà máy chế tạo chip (fabs).

3.

Wafer trong nhà máy chế tạo chip

Sau khi hoàn thiện phần nền, mỗi wafer sẽ được đưa vào các

dây chuyền chế tạo chip – nơi nó trải qua hơn 1000 bước xử lý trong nhiều

tháng. Các bước này bao gồm:

- Oxidation

– tạo lớp oxide mỏng cách điện trên bề mặt silicon

- Photolithography

– dùng ánh sáng chiếu qua mask để in mẫu mạch

- Etching

– khắc bỏ các vùng không mong muốn

- Ion

Implantation – bắn ion để thay đổi tính chất điện của silicon

- Deposition

– phủ các lớp kim loại, vật liệu cách điện, vật liệu bán dẫn

- Chemical

Mechanical Planarization (CMP) – đánh bóng lại bề mặt giữa các bước

Những bước này được lặp đi lặp lại hàng chục lần – vì con

chip hiện đại có thể có 30–50 lớp mạch xếp chồng.

Mỗi lớp trên wafer là một phần nhỏ trong cấu trúc khổng lồ:

transistor, dây nối, tụ điện, cổng logic, bộ nhớ...

4.

Wafer chứa bao nhiêu die?

Số lượng die (vi mạch riêng lẻ) trên một wafer phụ

thuộc vào các yếu tố:

- Kích

thước wafer (vd: 300 mm)

- Kích

thước die (vd: 10 mm², 50 mm²)

- Tỷ

lệ viền không sử dụng (edge loss) do hình tròn

- Khoảng

cách kỹ thuật giữa các die

- Tỷ

lệ hư hỏng (yield) do lỗi sản xuất

Ví dụ:

Với wafer 300 mm và die 50 mm², có thể sản xuất được khoảng 600

die.

Nếu yield là 80%, thì chỉ có khoảng 480 die đạt chuẩn – tức là

hơn 100 die bị loại bỏ vì lỗi.

Mỗi die lỗi có thể gây mất mát hàng chục đến hàng trăm USD, đặc biệt với

các chip cao cấp như CPU, GPU, SoC di động...

5.

Tại sao wafer càng lớn càng tốt?

Một nguyên tắc kinh tế cơ bản: wafer càng to → càng nhiều

die → càng rẻ chi phí sản xuất trên mỗi die.

Lợi ích của wafer lớn:

- Giảm

chi phí sản xuất mỗi die

- Tăng

hiệu suất chế tạo

- Ít

thao tác xử lý hơn để tạo ra cùng số lượng chip

Chính vì vậy, ngành công nghiệp đã dần chuyển từ 150 mm →

200 mm → 300 mm, và đã từng đặt nhiều kỳ vọng vào 450 mm wafer. Tuy

nhiên, wafer 450 mm hiện vẫn chưa phổ biến vì chi phí đầu tư thiết bị mới

quá cao và phức tạp kỹ thuật vượt trội.

6.

Một vài điều thú vị về Wafer

- Có

những wafer chỉ dùng để test quy trình (test wafer) – không chứa

die, chỉ kiểm tra lớp phủ, khắc, implant...

- Một

wafer hoàn thiện có thể trị giá hơn 10,000 USD – thậm chí cao hơn với

wafer EUV.

- Chiều

cao tổng các lớp mạch trên wafer chỉ khoảng 5–10 micromet – mỏng

hơn sợi tóc người.

- Wafer

rất mỏng và dễ vỡ – nhiều nhà máy phải dùng robot vận chuyển trong phòng sạch

cấp ISO 1.

7.

Wafer đi về đâu sau khi chế tạo?

Sau khi hoàn tất toàn bộ các bước chế tạo:

- Dicing

– wafer được cắt thành từng die riêng biệt bằng dao laser hoặc cưa

kim cương

- Testing

– mỗi die được kiểm tra bằng thiết bị probe station để xác định có

hoạt động tốt không

- Packaging

– các die đạt yêu cầu sẽ được đóng gói thành chip: Flip Chip, BGA, QFN,

WLCSP…

- Assembly

– chip được gắn lên bảng mạch (PCB), tích hợp vào các sản phẩm điện

tử cuối cùng như điện thoại, máy tính, xe điện...

8.

Mọi con chip đều bắt đầu từ một tấm gương silicon

Hành trình từ Wafer → Die → Flip Chip → Package → PCB →

Thiết bị điện tử là hành trình hàng tỷ con transistor hợp tác trong không

gian vài cm².

Mỗi lần bạn bật điện thoại, chơi game, xử lý ảnh hay gọi

video, hãy nhớ rằng: mọi thứ bắt đầu từ một tấm wafer tròn xoe và lặng lẽ

trong phòng sạch.

9.

Muốn hiểu sâu hơn?

Bạn từng thắc mắc vì sao mask có thể in hình lên wafer

chính xác đến nanomet?

Hay muốn biết làm sao để một con chip được "thu hoạch" hiệu quả từ

wafer mà không hỏng hóc?

Hãy đón đọc những bài viết tiếp theo trong chuỗi truyền

thông kỹ thuật của IC Academy – nơi kiến thức vi mạch trở nên gần gũi và hấp

dẫn hơn bao giờ hết.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận