Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

UVM - Phương pháp xác minh phần cứng tiêu chuẩn công nghiệp

UVM (Universal Verification Methodology) là một phương pháp xác minh tiêu chuẩn công nghiệp được phát triển nhằm kiểm thử các thiết kế phần cứng (Design Under Test - DUT) được mô tả bằng các ngôn ngữ mô tả phần cứng như Verilog hoặc VHDL. Phương pháp này được chuẩn hóa bởi IEEE theo tiêu chuẩn IEEE 1800.2.

UVM là một thư viện lớp (class library) được xây dựng trên nền SystemVerilog, khai thác tối đa các đặc tính của lập trình hướng đối tượng (OOP) như kế thừa, đa hình, và trừu tượng hóa. Mặc dù hiện nay thư viện UVM không phải là mã nguồn chuẩn hóa chính thức bởi IEEE, nhưng nó được phát triển và bảo trì bởi tổ chức phi lợi nhuận Accellera Systems Initiative, và có thể được sử dụng miễn phí cùng với các phần mềm mô phỏng như QuestaSim, VCS, hoặc XSIM.

Mục tiêu của UVM

Mục tiêu của UVM

UVM hướng đến việc xây dựng các testbench tái sử dụng, có tính mở rộng cao và dễ cấu hình, phù hợp với các dự án thiết kế vi mạch phức tạp trong môi trường công nghiệp. Thư viện này không chỉ mang lại sự chuẩn hóa trong quy trình xác minh, mà còn giúp tăng năng suất và giảm chi phí kiểm thử nhờ tính khả chuyển giữa các dự án.

Kiến trúc tổng thể của UVM Testbench

Kiến trúc tổng thể của UVM Testbench

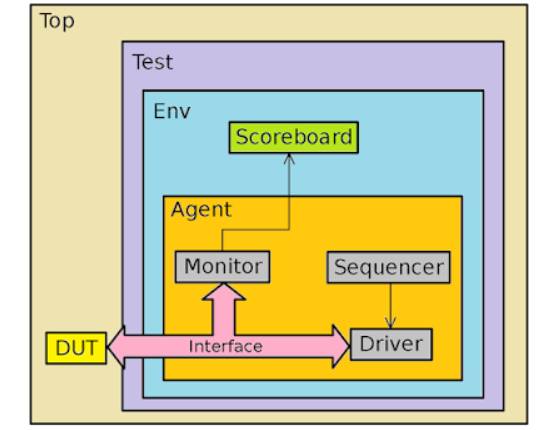

Một môi trường UVM điển hình bao gồm các thành phần chính sau:

→ Thiết kế phần cứng cần xác minh – trong ví dụ này là UART-APB IP Core.

→ Lớp bao toàn bộ môi trường xác minh, chứa các thiết lập test cụ thể.

→ Gồm các thành phần phụ như

UVM Agent, UVM Scoreboard, hoặc các UVM Environment con.→ Quản lý kết nối và tương tác với DUT, bao gồm ba phần chính:

- UVM Driver: Nhận transaction từ Sequencer, chuyển thành tín hiệu điều khiển DUT.

- UVM Sequencer: Điều phối quá trình truyền transaction từ các sequence.

- UVM Monitor: Giám sát tín hiệu giao tiếp với DUT, thu thập dữ liệu để phân tích.

→ So sánh dữ liệu thực tế với kết quả mong đợi, dùng để kiểm tra tính đúng đắn của DUT.

→ Tạo ra các transaction (giao dịch), mô phỏng các hành vi đầu vào cho DUT.

→ Gói dữ liệu dùng để mô tả các hành vi kiểm thử.

Lý do nên áp dụng UVM trong xác minh thiết kế số

Lý do nên áp dụng UVM trong xác minh thiết kế số

Chuẩn hóa quy trình xác minh (Verification Flow)

Chuẩn hóa quy trình xác minh (Verification Flow) Khả năng mở rộng và tái sử dụng cao

Khả năng mở rộng và tái sử dụng cao Hỗ trợ kiểm thử theo hướng đối tượng

Hỗ trợ kiểm thử theo hướng đối tượng Dễ dàng tích hợp với hệ thống CI/CD cho chip design

Dễ dàng tích hợp với hệ thống CI/CD cho chip design Tương thích với nhiều công cụ mô phỏng phổ biến

Tương thích với nhiều công cụ mô phỏng phổ biến

Thảo luận và học hỏi thêm

Thảo luận và học hỏi thêm

Nếu bạn đang nghiên cứu hoặc làm việc trong lĩnh vực thiết kế & xác minh phần cứng (DV - Design Verification), hãy chia sẻ kinh nghiệm hoặc câu hỏi của bạn trong phần bình luận! Việc áp dụng UVM đúng cách sẽ mang lại lợi thế kỹ thuật đáng kể trong các dự án SoC, ASIC hoặc FPGA.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận