Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

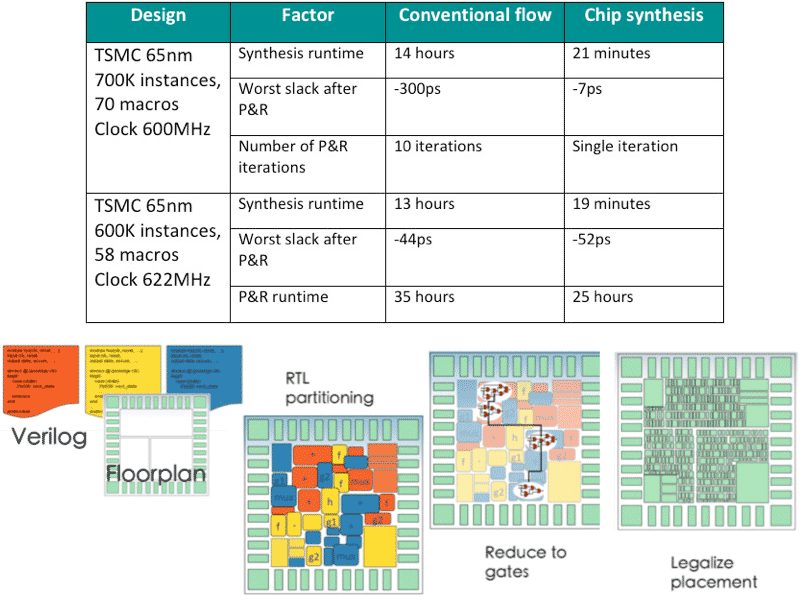

Tổng hợp chip: Một phương pháp mới cho thực thi RTL

Tổng hợp chip là phương pháp mới nhằm biến mã RTL (cấp truyền thanh) thành cổng cho cả một con chip cùng lúc.

Hạn chế của tổng hợp truyền thống

Tổng hợp truyền thống gặp nhiều khó khăn, đặc biệt với thiết kế trên 20 triệu cổng. Phương pháp này phụ thuộc vào tối ưu hóa ở cấp cổng, nên chỉ xử lý được các khối nhỏ và buộc người thiết kế chia thiết kế thành nhiều khối nhỏ. Tuy nhiên, vì nơi ghép và định tuyến có thể xử lý khối lớn hơn, các khối tổng hợp lại được gộp thành các khối lớn. Nhưng việc quản lý thời gian và ràng buộc qua quá trình ghép các khối lại rất phức tạp, làm cho tổng hợp truyền thống trở nên bất khả thi.

Tổng hợp: Một chút lịch sử

Ban đầu, công cụ tổng hợp chỉ chuyển mã RTL thành cổng bằng cách sử dụng các thuật toán đơn giản, sau đó tối ưu hóa cổng để đạt các ràng buộc. Công cụ tổng hợp cũ được xây dựng quanh việc tối ưu hóa cổng, và chỉ lấy vị trí vật lý vào lúc tối ưu hóa ở cấp cổng. Nhưng khi thông tin vật lý trở nên quan trọng hơn, vị trí được kết hợp vào tối ưu hóa cổng để ước tính các yếu tố như điện trở.

Nhược điểm của cách tiếp cận truyền thống

Có hai nhược điểm lớn của tối ưu hóa cổng: thứ nhất, nó là tối ưu hóa cấp thấp; thứ hai, cần khối lượng dữ liệu lớn. Do đó, thời gian chạy quá dài và công suất xử lý hạn chế. Kết quả là thiết kế phải chia nhỏ ra thành khối nhỏ để phù hợp với công cụ. Với chip có 100 triệu cổng, cần chia thành 200 khối, gây khó khăn trong việc kiểm soát và tạo ra các ràng buộc thời gian.

Giải pháp tổng hợp chip

Tổng hợp chip hoạt động khác biệt: mã RTL được phân chia thành các phần dựa trên kết nối, mỗi phần đủ nhỏ để không chứa dây dẫn dài, tránh sự biến động lớn về thời gian. Cách tiếp cận này giúp tiết kiệm tài nguyên bộ nhớ và cho phép tổng hợp nhanh hơn, hiệu quả hơn. Tổng hợp chip còn đưa vị trí vào trong bước tổng hợp RTL, cho phép tối ưu hóa ở cấp cao.

So sánh tổng hợp chip và truyền thống

Một ví dụ cụ thể với thiết kế 700K tại tiến trình 65nm của TSMC cho thấy tổng hợp truyền thống mất hơn 14 giờ và cần 10 lần lặp với thời gian 20 tuần, còn tổng hợp chip chỉ cần 20 phút và hoàn tất trong một lần lặp với kết quả tốt hơn.

Tổng hợp chip và công nghệ tổng hợp cấp cao (HLS)

Tổng hợp chip là mắt xích còn thiếu trong phương pháp HLS. Các công cụ HLS chỉ có góc nhìn thô về các yếu tố thiết kế, nhưng với tổng hợp truyền thống thì việc khám phá không gian thiết kế chậm chạp. Tổng hợp chip cho tốc độ và độ chính xác cao, cho phép HLS áp dụng trong nhiều loại thiết kế hơn.

Kết quả

Tổng hợp chip nhanh hơn 20-100 lần so với công cụ tổng hợp phổ biến, đạt chất lượng kết quả tương đương hoặc tốt hơn, và cung cấp vị trí có thể chạy mượt qua công cụ định tuyến và bố trí chuẩn. Nó có khả năng xử lý các thiết kế chip lên tới 100 triệu cổng.

Tóm tắt

Tổng hợp chip vượt trội so với tổng hợp truyền thống nhờ vào khả năng tổng hợp và tối ưu hóa toàn bộ chip một lúc, thay vì ép người thiết kế chia nhỏ thiết kế thành nhiều khối. Công nghệ chủ chốt là tối ưu hóa ở cấp RTL thay vì cấp cổng, cho phép khám phá thiết kế nhanh và hiệu quả hơn, đồng thời vị trí thiết kế được xác định chính xác hơn, giúp cho dự đoán trở nên nhất quán.

Nguồn: Thời báo Điện - Điện tử

Biên dịch bởi Admin từ iCdemy.com - Đào tạo thiết kế vi mạch chuyên sâu

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận