Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

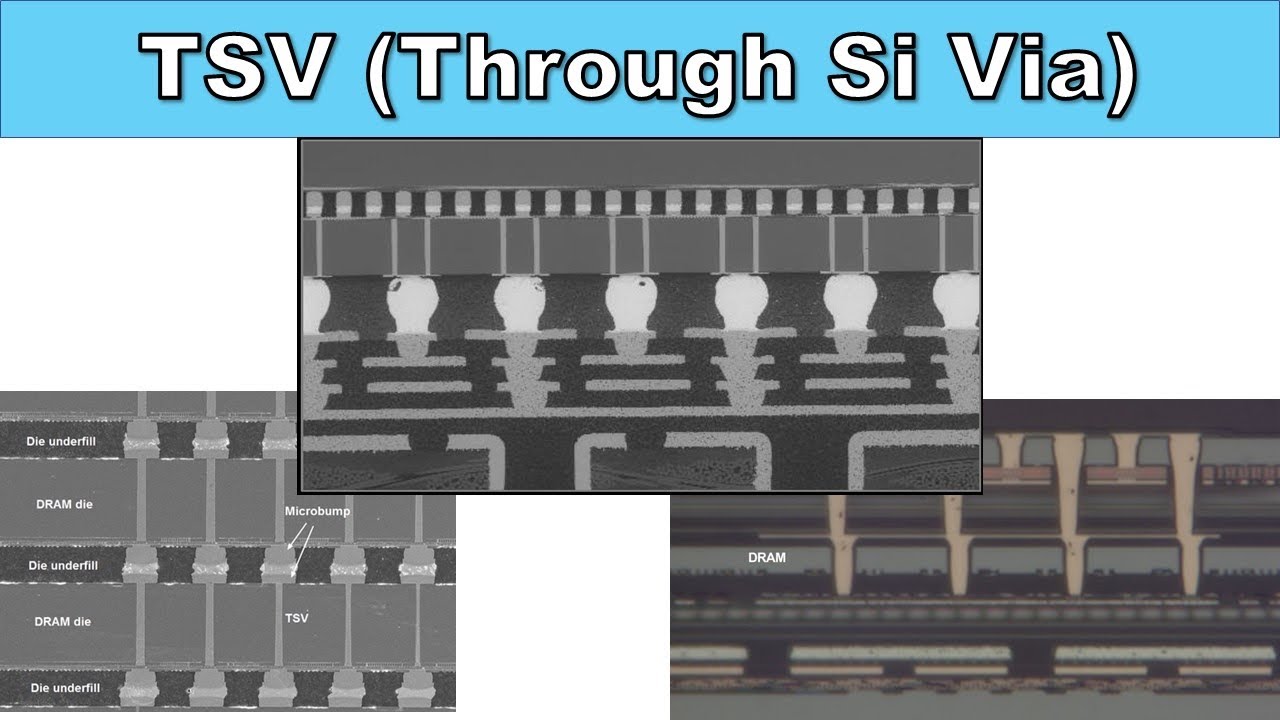

TSV – CỘT SỐNG CỦA CHIP 3D

Bạn có thể xây một tòa nhà cao tầng để tiết kiệm diện tích đất.

Vậy tại sao không “xếp tầng” cả con chip?

Đó chính là ý tưởng đằng sau 3D IC – và TSV (Through-Silicon Via) chính là

thang máy kết nối các tầng silicon lại với nhau.

1. TSV là

gì?

TSV (vi nghĩa: lỗ xuyên silicon) là các ống dẫn siêu nhỏ được khoan dọc xuyên

qua lớp silicon của một con chip (die), sau đó được lấp đầy bằng kim loại như đồng

(Cu) để dẫn điện.

Nó kết nối trực tiếp từ mặt trước đến mặt sau của một die, cho phép truyền tín

hiệu và nguồn giữa nhiều lớp chip xếp chồng – thay vì đi vòng qua dây hoặc bump

như thiết kế 2D truyền thống.

So với microbump hay wire bonding, TSV:

- Ngắn

hơn: đường truyền tín hiệu chỉ vài chục micromet → giảm trễ

- Mạnh

hơn: truyền nguồn và tín hiệu song song với mật độ cao

- Thẳng

hơn: nối dọc trực tiếp → tiết kiệm diện tích mặt phẳng

2. Cấu

trúc của một TSV gồm những gì?

- Lỗ

khoan: tạo bằng phương pháp dry etching (khắc khô), thường có đường

kính 2–10 µm

- Lớp

cách điện (liner): thường là SiO₂ để

cách ly TSV với silicon xung quanh

- Ruột

kim loại: đồng (Cu) được mạ vào trong để dẫn điện

- Lớp

barrier và seed: lớp chắn chống khuếch tán và giúp quá trình mạ điện

diễn ra đều

- Redistribution

Layer (RDL): tầng định tuyến giúp kết nối từ TSV đến bump hoặc mạch

3. TSV được

dùng ở đâu?

- HBM

(High Bandwidth Memory): bộ nhớ DRAM xếp tầng, truyền dữ liệu siêu

nhanh

- 3D

SoC: tích hợp logic + DRAM + analog trong cùng một khối

- Image

Sensor cao cấp: nối cảm biến ảnh với mạch xử lý ngay bên dưới → ảnh xử

lý nhanh hơn, rõ hơn

- Interposer

2.5D: dùng trong chiplet để kết nối nhiều die qua cầu silicon

- AI

Accelerator, HPC, 5G: nơi cần tốc độ truyền cao, mật độ kết nối dày đặc,

độ trễ cực thấp

4. Vì sao

TSV là công nghệ quan trọng?

- Rút

ngắn đường truyền: từ vài mm → vài chục µm

- Tiết

kiệm diện tích: stacking thay vì spreading

- Tăng

mật độ kết nối: hàng ngàn TSV trong một chip

- Ghép

nhiều công nghệ: DRAM + Logic + RF + Analog

- Giảm

tiêu thụ điện: do giảm chiều dài đường dây và điện cảm

5. Một ví

dụ nhỏ:

Một AI chip cần giao tiếp với bộ nhớ DRAM cực nhanh. Nếu

dùng PCB truyền thống, tín hiệu phải đi xa, chậm và nhiễu.

Nhưng nếu xếp chồng DRAM ngay trên logic và nối bằng TSV, băng thông có thể

tăng gấp 10 lần, độ trễ giảm tới 80%.

Hoặc:

Camera smartphone hiện đại dùng TSV để nối cảm biến ảnh với vi xử lý ngay bên

dưới, giảm kích thước cụm camera và tăng khả năng xử lý ảnh theo thời gian thực.

6. Nhưng

có phải TSV luôn là lựa chọn tốt nhất?

Không hẳn.

- Chi

phí chế tạo TSV rất cao, yêu cầu fab và mask đặc biệt

- Tỷ lệ

lỗi khi tạo TSV có thể gây ngắt mạch, mất kết nối

- Tản

nhiệt trở nên khó khăn khi stacking nhiều tầng

- Việc

thiết kế và routing cần công cụ EDA chuyên biệt, không thể dùng như layout

2D truyền thống

7. Kết luận:

TSV không chỉ là một “cột dây dẫn điện”. Nó là cột sống của

hệ sinh thái 3D IC hiện đại.

Không có TSV → không có HBM, không có chiplet tốc độ cao, không có stacking

trong AI accelerator, smartphone hay hệ thống HPC.

TSV cho phép bạn xây con chip như một tòa nhà nhiều tầng – mỗi

tầng có chức năng riêng, hiệu năng riêng – nhưng cùng phối hợp hoàn hảo qua các

“ống dẫn dọc” chính giữa.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận