Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

Thiết kế vi mạch: Ký Sinh Là Gì? Tác Động và Cách Giảm Thiểu Trong IC

Trong

thiết kế mạch tích hợp (IC), ký sinh là một yếu tố không thể tránh khỏi nhưng

có thể gây ra nhiều vấn đề nếu không được kiểm soát. Ký sinh xuất hiện dưới dạng

điện dung, điện trở và độ tự cảm không mong muốn, làm chậm mạch, thay đổi đáp ứng

tần số hoặc gây nhiễu. Bài viết này sẽ phân tích các loại ký sinh, nguồn gốc, ảnh

hưởng đến mạch, cách giảm thiểu chúng, đặc biệt trong các ứng dụng tần số cao,

và vai trò của giao tiếp với nhà thiết kế mạch.

Ký Sinh Là Gì và Tại Sao Chúng

Quan Trọng?

Ký

sinh trong IC là các thành phần điện không mong muốn xuất hiện do cấu trúc vật

lý của chip. Khi các lớp kim loại chồng lên nhau, bóng bán dẫn được đặt gần

nhau, hoặc cấy ghép nằm trong chất nền, ký sinh được tạo ra, bao gồm điện dung,

điện trở và độ tự cảm. Những thành phần này có thể làm giảm hiệu suất mạch, đặc

biệt trong các thiết kế tần số cao (≥20 MHz), nơi mà ký sinh có thể “giết chết”

chip nếu không được kiểm soát.

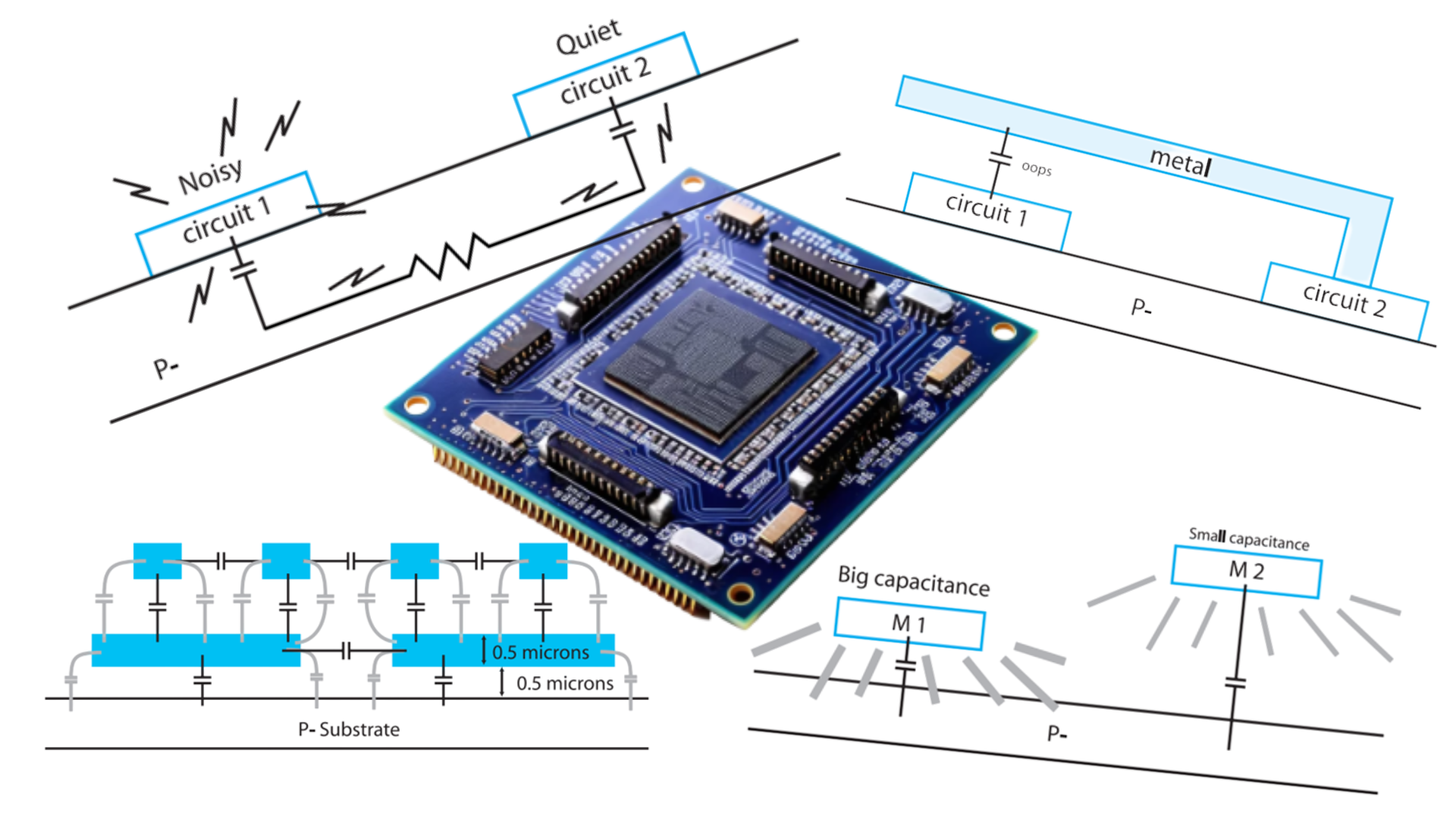

Ví

dụ, ký sinh xuất hiện khi kim loại chạy trên kim loại khác, tạo ra điện dung giống

như một tụ điện nhỏ. Tương tự, dòng điện chạy qua dây dẫn tạo ra điện trở ký

sinh, gây sụt áp (IR drop). Những yếu tố này làm chậm thời gian đáp ứng, giảm

băng thông hoặc gây nhiễu giữa các khối mạch. Do đó, nhà thiết kế mặt nạ cần hiểu

rõ chức năng mạch và phối hợp với nhà thiết kế mạch để giảm thiểu ảnh hưởng của

ký sinh.

Các Loại Ký Sinh và Nguồn Gốc

1. Điện Dung Ký Sinh

Điện

dung ký sinh xuất hiện ở mọi nơi trong IC. Bất kỳ hai vật liệu dẫn điện nào gần

nhau—như dây kim loại song song, cấy ghép trong chất nền, hoặc kim loại với chất

nền—đều tạo ra điện dung ký sinh. Ví dụ, bốn đường kim loại chạy trên hai đường

khác có thể tạo ra nhiều tụ điện tấm song song, cùng với điện dung từ kim loại

xuống chất nền và điện dung rìa.

- Mức

độ: Điện dung ký sinh thường nhỏ, khoảng 10 femtofarad (fF) cho một dây

kim loại dày 0,5 µm cách chất nền 0,5 µm. Tuy nhiên, tổng hợp nhiều điện

dung nhỏ này có thể ảnh hưởng lớn đến hiệu suất.

- Tác

động: Ở tần số cao, ký sinh làm chậm mạch, giảm băng thông hoặc gây nhiễu.

Ví dụ, một bộ khuếch đại tần số cao có thể mất 10% băng thông nếu không

tính đến điện dung ký sinh.

- Cách

giảm:

- Rút

ngắn dây: Giảm chiều dài dây dẫn để giảm diện tích chồng lấn, từ đó giảm

điện dung ký sinh.

- Chọn

kim loại xa chất nền: Kim loại cấp cao (Metal 2, 3, 4) thường có điện

dung thấp hơn do khoảng cách lớn hơn tới chất nền. Tuy nhiên, cần tính

toán cụ thể dựa trên hướng dẫn quy trình (process manual), vì chiều rộng

tối thiểu của kim loại có thể làm tăng điện dung.

- Ví

dụ: Trong một quy trình, Metal 2 có điện dung thấp nhất (24 fF cho dây 10

µm) do cân bằng giữa khoảng cách và chiều rộng tối thiểu, dù Metal 4 xa

chất nền hơn nhưng có chiều rộng lớn hơn.

Lưu

ý: Điện dung ký sinh tới chất nền đặc biệt nguy hiểm vì chất nền kết nối toàn bộ

chip, truyền nhiễu giữa các mạch. Ví dụ, nhiễu từ mạch 1 có thể ảnh hưởng đến mạch

2 qua chất nền nếu không được kiểm soát.

2. Điện Trở Ký Sinh

Điện

trở ký sinh xuất hiện trong mọi dây dẫn, đặc biệt trong dây nguồn hoặc dây dài,

gây sụt áp (IR drop). Ví dụ, một dây 2 mm, rộng 2 µm, có điện trở 50 Ω, mang

dòng 1 mA sẽ gây sụt áp 50 mV. Nếu mạch nhạy cảm với điện áp, điều này có thể

làm hỏng hiệu suất.

- Ảnh

hưởng: Điện trở ký sinh đặc biệt quan trọng trong dây nguồn, nơi dòng điện

lớn (20-30 mA) có thể gây sụt áp đáng kể.

- Cách

giảm:

- Tăng

chiều rộng dây: Ví dụ, tăng từ 2 µm lên 10 µm để giảm sụt áp từ 50 mV xuống

10 mV, đáp ứng yêu cầu mạch.

- Sử

dụng kim loại dày: Kim loại có điện trở thấp trên ô vuông (ohm/square)

giúp giảm ký sinh. Tham khảo hướng dẫn quy trình để chọn kim loại phù hợp.

- Song

song kim loại: Kết nối nhiều lớp kim loại song song để giảm điện trở tổng,

đặc biệt hữu ích cho dây nguồn.

- Tùy

chọn dây nguồn: Chia nhỏ dây nguồn hoặc dùng dây riêng cho khối tiêu thụ

dòng lớn (ví dụ, 10 mA) để tránh ảnh hưởng đến các khối khác.

Nguyên

tắc: Nếu sụt áp do điện trở ký sinh vượt quá 10 mV, cần kiểm tra với nhà thiết

kế mạch để đảm bảo hiệu suất.

3. Độ Tự Cảm Ký Sinh

Độ

tự cảm ký sinh trở nên đáng kể ở tần số rất cao, khi dây dẫn hoạt động như cuộn

cảm. Điều này đặc biệt quan trọng trong các mạch tần số cao, nơi ký sinh có thể

gây ghép cảm ứng giữa các dây.

- Cách

xử lý:

- Mô

hình hóa độ tự cảm ký sinh ngay từ đầu, phối hợp với nhà thiết kế mạch để

xác định chiều dài và vị trí dây.

- Sử

dụng dây rộng hơn hoặc để khoảng trống quanh dây nhạy cảm để tránh ghép cảm

ứng.

- Làm

việc trên sơ đồ mặt bằng (floorplan) từ sớm để tính toán ký sinh chính

xác.

Ảnh

Hưởng của Ký Sinh lên Mạch

Ký

sinh ảnh hưởng đến hiệu suất mạch theo nhiều cách:

- Mạch

tần số cao: Điện dung ký sinh và độ tự cảm ký sinh làm giảm băng thông,

gây chậm trễ hoặc nhiễu. Ở tần số ≥20 MHz, việc bỏ qua ký sinh có thể làm

hỏng chip.

- Mạch

nhạy cảm: Một số mạch, như bộ khuếch đại, đặc biệt nhạy cảm với điện dung

ký sinh ở đầu vào, yêu cầu dây ngắn nhất có thể.

- Mạch

nguồn: Điện trở ký sinh trong dây nguồn gây sụt áp, ảnh hưởng đến hiệu suất

các khối mạch.

Để

giảm thiểu ký sinh, nhà thiết kế mặt nạ cần hiểu rõ chức năng mạch thông qua

giao tiếp với nhà thiết kế mạch. Ba câu hỏi chính cần đặt ra là:

- Chức

năng của mạch là gì? (Xác định mức độ nhạy cảm với ký sinh).

- Mạch

xử lý bao nhiêu dòng điện? (Tính toán chiều rộng dây và sụt áp).

- Có

yêu cầu đặc biệt nào không? (Ví dụ, dây ngắn, kim loại cụ thể).

Kỹ Thuật Giảm Thiểu Ký Sinh

1. Rút Ngắn Dây Dẫn

Giảm

chiều dài dây là cách đơn giản nhất để giảm điện dung ký sinh và điện trở ký

sinh. Dây ngắn hơn giảm diện tích chồng lấn với chất nền hoặc các dây khác, từ

đó giảm ký sinh. Ví dụ, trong một bộ khuếch đại tần số cao, nhà thiết kế có thể

yêu cầu dây đầu vào ngắn nhất có thể để giảm điện dung ký sinh.

2. Chọn Kim Loại Phù Hợp

Lựa

chọn kim loại là yếu tố quan trọng để giảm ký sinh. Kim loại cấp cao (Metal 2,

3, 4) thường có điện dung ký sinh thấp hơn do xa chất nền, nhưng cần tính toán

cụ thể. Ví dụ:

- Quy

trình mẫu: Metal 1 (gần chất nền) có điện dung 0,1 fF/µm², trong khi Metal

2, 3, 4 lần lượt là 0,08, 0,06, 0,04 fF/µm². Tuy nhiên, chiều rộng tối thiểu

tăng (0,8 µm cho Metal 1, 2; 2,4 µm cho Metal 3; 6,5 µm cho Metal 4), làm

tăng diện tích và có thể tăng điện dung ký sinh.

- Kết

quả: Metal 2 có thể là lựa chọn tối ưu (24 fF cho dây 10 µm) do cân bằng

giữa khoảng cách và diện tích.

Lưu

ý: Luôn tham khảo hướng dẫn quy trình để tính toán ký sinh thay vì giả định kim

loại cấp cao luôn tốt hơn.

3. Định Tuyến Thông Minh

Trong

thiết kế analog, tránh chạy dây qua khối mạch nhạy cảm để giảm điện dung ký

sinh. Thay vào đó, định tuyến dây xung quanh khối hoặc sử dụng dây riêng cho

các nút nhạy cảm. Trong thiết kế số, ký sinh thường xuất hiện do dây chồng lên

nhau, vì vậy cần giám sát bộ định tuyến tự động để tránh nhiễu.

- Ví

dụ: Trong một mảng mạch, dây nguồn cung cấp 19 mA có thể được thu hẹp dần

từ 38 µm ở đầu vào xuống 11 µm ở cuối để tiết kiệm không gian, hoặc dùng

dây riêng cho khối tiêu thụ 10 mA để tránh sụt áp ảnh hưởng đến các khối

khác.

4. Tùy Chỉnh Thiết Bị

- CMOS:

Chia nhỏ cổng (gate fingers) để giảm điện trở ký sinh nối tiếp và hằng số

thời gian RC. Ví dụ, chia một cổng thành hai ngón tay song song giảm điện

trở xuống 1/4, cải thiện tốc độ.

- Bipolar:

Gộp các cực thu để giảm điện dung ký sinh tới chất nền. Ví dụ, kết hợp nhiều

bóng bán dẫn lưỡng cực vào một giếng N chung để giảm diện tích và ký sinh.

5. Sử Dụng Ký Sinh Có Lợi (Hiếm)

Dù

ký sinh thường có hại, một số trường hợp có thể tận dụng chúng. Ví dụ, chạy dây

nguồn và dây đất chồng lên nhau tạo điện dung ký sinh miễn phí, hỗ trợ tách

ghép nguồn. Tuy nhiên, không nên dựa vào ký sinh do sự biến đổi lớn (±50%), có

thể làm hỏng mạch nếu không được kiểm soát.

Cân Nhắc Đặc Biệt cho Tần Số

Cao

Ở

tần số cao (≥20 MHz), ký sinh trở nên cực kỳ quan trọng. Điện dung ký sinh và độ

tự cảm ký sinh có thể làm giảm băng thông, gây chậm trễ hoặc nhiễu, đặc biệt

trong các mạch như bộ khuếch đại hoặc bộ dao động. Nhà thiết kế mặt nạ cần:

- Làm

việc trên sơ đồ mặt bằng từ sớm để tính toán ký sinh.

- Phối

hợp với nhà thiết kế mạch để xác định dây nhạy cảm và áp dụng kỹ thuật như

dây ngắn, kim loại cấp cao hoặc khoảng trống để giảm ghép cảm ứng.

Giao Tiếp với Nhà Thiết Kế Mạch

Giao

tiếp là chìa khóa để kiểm soát ký sinh. Nhà thiết kế mặt nạ cần đặt câu hỏi về

chức năng mạch, yêu cầu dòng điện và độ nhạy với ký sinh. Ví dụ:

- “Mạch

này có nhạy cảm với điện dung ký sinh ở đầu vào không?”

- “Sụt

áp 50 mV trên dây này có chấp nhận được không?”

Nhà

thiết kế mạch có thể yêu cầu các kỹ thuật cụ thể, như sử dụng Metal 2 hoặc rút

ngắn dây. Bằng cách học hỏi từ nhà thiết kế mạch và kinh nghiệm thực tế, nhà

thiết kế mặt nạ có thể đưa ra quyết định chủ động để giảm ký sinh.

Kết Luận

Ký

sinh là thách thức không thể tránh khỏi trong thiết kế IC, nhưng có thể được kiểm

soát thông qua:

- Tính

toán cẩn thận dựa trên hướng dẫn quy trình.

- Lựa

chọn kim loại và định tuyến thông minh (rút ngắn dây, dùng Metal 2, thu hẹp

dây nguồn).

- Tùy

chỉnh thiết bị (chia cổng CMOS, gộp cực thu Bipolar).

- Giao

tiếp chặt chẽ với nhà thiết kế mạch để hiểu chức năng và yêu cầu.

Bằng cách hiểu rõ ký sinh và áp dụng các kỹ thuật phù hợp, nhà thiết kế mặt nạ có thể tối ưu hóa hiệu suất mạch, đặc biệt trong các ứng dụng tần số cao. Hãy luôn sáng tạo, đặt câu hỏi và học hỏi từ thực tế để kiểm soát ký sinh hiệu quả.

#ThiếtKếViMạch #KýSinhTrongIC #ICDesign #ParasiticEffects #AnalogLayout #HighFrequencyDesign #CustomLayout #VLSI #ChipDesign #LayoutOptimization

Thẻ:

ThiếtKếViMạch KýSinhTrongIC ICDesign ParasiticEffects AnalogLayout HighFrequencyDesign CustomLayout VLSI ChipDesign LayoutOptimization0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận