Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

Thiết kế vi mạch: Hiểu nhanh timescale trong Verilog/SystemVerilog

Trong

quá trình lập trình mô phỏng với Verilog hoặc SystemVerilog, bạn sẽ thường gặp

dòng timescale ở đầu mỗi file. Với nhiều bạn mới học, dòng này có thể bị bỏ qua

vì tưởng không quan trọng. Tuy nhiên, sự thật là timescale đóng vai trò cực kỳ

quan trọng trong việc xác định cách thời gian được hiểu và xử lý trong mô phỏng.

Bài

viết này sẽ giúp bạn hiểu nhanh timescale, cách sử dụng đúng, và lý do vì sao

nó ảnh hưởng trực tiếp đến kết quả mô phỏng RTL.

1. timescale

là gì?

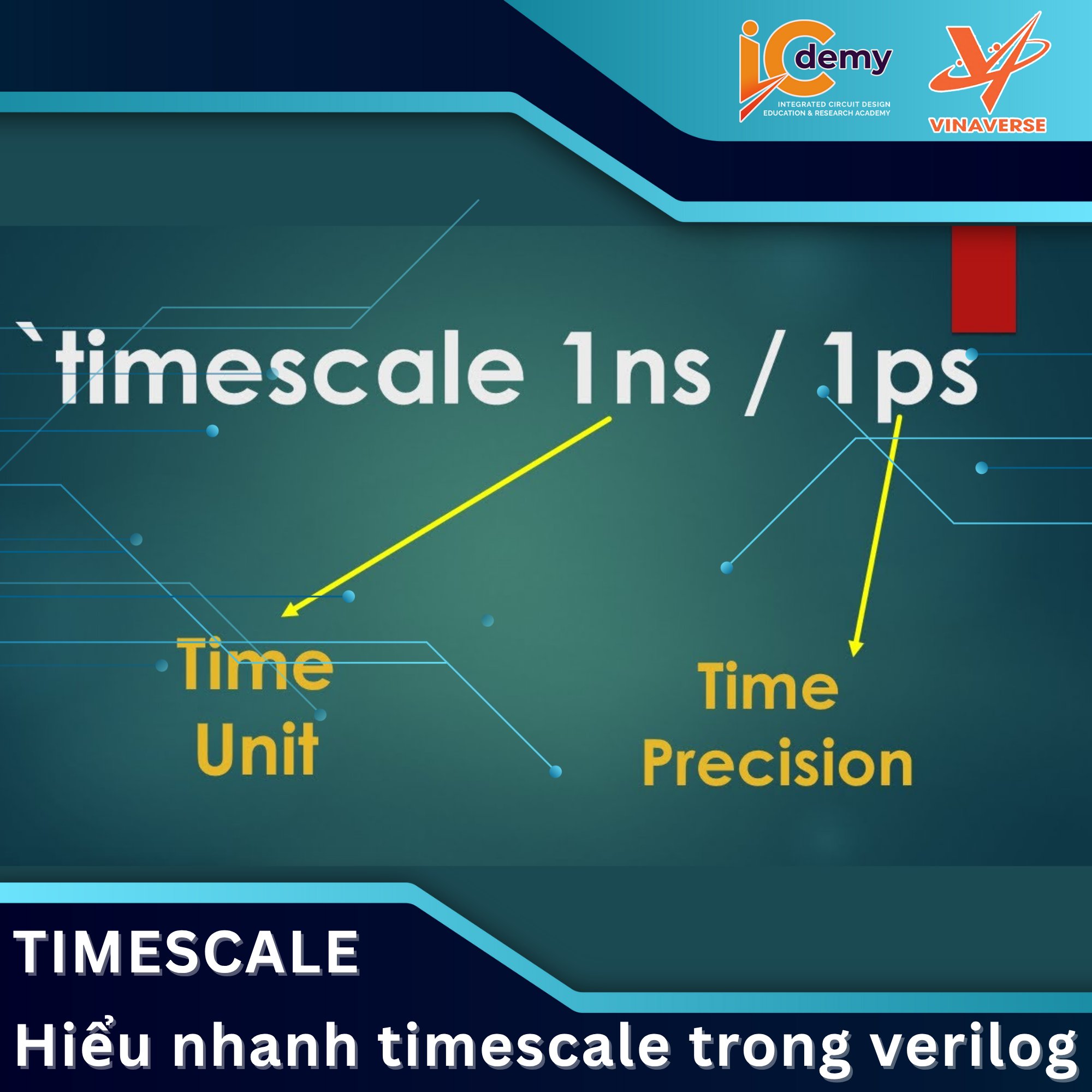

timescale là một

chỉ thị dành cho trình mô phỏng trong Verilog/SystemVerilog. Nó định nghĩa hai

yếu tố:

- Đơn vị thời gian (time unit): xác định độ dài thực tế của các

giá trị delay như #1.

- Độ chính xác thời gian (time

precision): mức độ

chi tiết nhỏ nhất mà trình mô phỏng sử dụng để tính toán và hiển thị thời

gian.

Cú pháp:

`timescale <time_unit>

/ <time_precision>

Ví dụ:

`timescale 1ns

/ 1ps

Câu lệnh trên

có nghĩa là: #1 tương đương với 1 nanosecond, và thời gian mô phỏng có thể được

tính chính xác tới từng picosecond.

2. Ý nghĩa

và ảnh hưởng của timescale

Giả sử bạn viết

dòng lệnh sau trong testbench:

#10;

Nếu không có timescale,

bạn hoàn toàn không biết 10 ở đây tương đương bao nhiêu thời gian thật. Nó có

thể là 10 nanosecond, 10 picosecond, hoặc thậm chí 10 millisecond, tùy theo định

nghĩa timescale ở đầu file.

Ví dụ:

`timescale 10ns

/ 1ns

#2; // Delay tương đương 20ns

Nếu bạn không định

nghĩa đúng timescale, kết quả mô phỏng có thể bị sai lệch nghiêm trọng. Điều

này ảnh hưởng trực tiếp đến:

- Waveform (biểu đồ tín hiệu)

- Logic timing

- Độ chính xác của chu kỳ clock và

delay

- Quá trình debug

Trong những dự

án phức tạp, chỉ một lỗi nhỏ trong timescale cũng có thể khiến bạn mất hàng giờ

để tìm ra nguyên nhân sai lệch trong mô phỏng.

3. Mẹo sử dụng

timescale hiệu quả

Để tránh những

rắc rối không đáng có, hãy lưu ý một số nguyên tắc khi làm việc với timescale:

- Luôn khai báo timescale ở đầu mỗi

file Verilog hoặc SystemVerilog.

Điều này giúp trình mô phỏng biết cách diễn giải các delay đúng ngay từ đầu.

- Đảm bảo tất cả các module và

testbench trong cùng một dự án dùng chung timescale. Nếu không, việc so sánh thời gian

giữa các module sẽ không nhất quán.

- Nếu làm việc nhóm hoặc sử dụng nhiều

file mô phỏng, hãy

định nghĩa timescale thống nhất trong một file cấu hình simulator, nếu

simulator của bạn hỗ trợ.

4. Kết luận

timescale là một

kiến thức tưởng chừng đơn giản nhưng lại có ảnh hưởng lớn trong mô phỏng RTL.

Nó là cơ sở để bạn hiểu rõ các giá trị delay, chu kỳ clock, và phản ứng tín hiệu

trong thiết kế số.

Sử dụng đúng timescale

sẽ giúp bạn:

- Có kết quả mô phỏng chính xác hơn

- Dễ dàng phân tích waveform

- Giảm thiểu lỗi khó debug

- Đảm bảo thiết kế hoạt động đúng với

mong đợi

Nếu bạn từng gặp

lỗi do thiếu hoặc đặt sai timescale, hẳn bạn sẽ hiểu vì sao đây là một phần

không thể bỏ qua trong bất kỳ dự án mô phỏng nào.

Bạn đã từng

quên hoặc định nghĩa sai timescale chưa? Hãy chia sẻ trải nghiệm của bạn để

cùng rút ra bài học nhé.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận