Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

Thiết kế SoC: Tương lai của NoC sẽ ra sao?

Thiết kế SoC: Tương lai của NoC sẽ ra sao?

Các hệ thống trên chip (SoC) cao cấp ngày nay phụ thuộc rất nhiều vào công nghệ mạng trên chip (NoC) tinh vi để đạt được hiệu suất và khả năng mở rộng. Khi nhu cầu về trí tuệ nhân tạo (AI), tính toán hiệu suất cao (HPC) và các ứng dụng tính toán chuyên sâu khác tiếp tục phát triển, việc thiết kế thế hệ SoC tiếp theo sẽ cần đến những giải pháp NoC thông minh và hiệu quả hơn để đáp ứng những thách thức này.

Mặc dù những tiến bộ này mang lại nhiều cơ hội hấp dẫn, nhưng chúng cũng đi kèm với những trở ngại đáng kể. Các nhà thiết kế SoC phải đối mặt với sự mở rộng nhanh chóng trong kiến trúc, áp lực về thời gian đưa sản phẩm ra thị trường, sự khan hiếm chuyên gia, việc sử dụng tài nguyên chưa tối ưu và các công cụ thiết kế rời rạc.

Sự tăng trưởng theo cấp số nhân của độ phức tạp trong thiết kế SoC

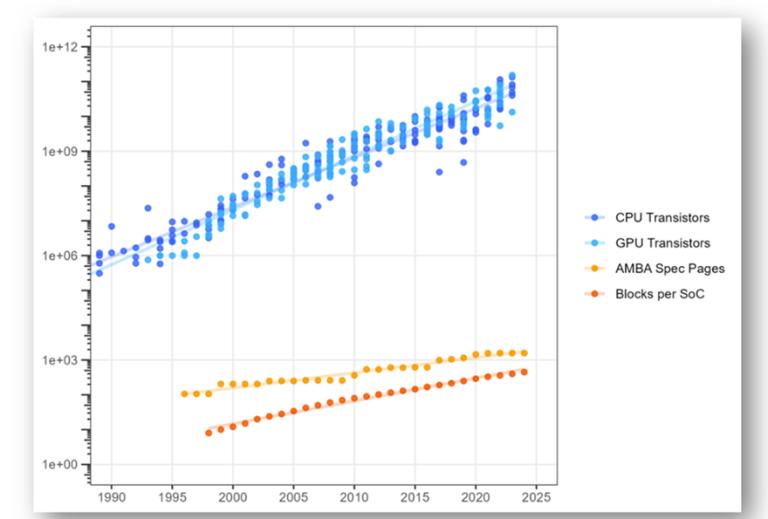

Thiết kế SoC đã đạt đến mức độ phức tạp chưa từng có, được thúc đẩy bởi những tiến bộ trong công nghệ xử lý và công cụ thiết kế. Hiện nay, các SoC thường bao gồm từ 50 đến hơn 500 khối IP, từ lõi vi xử lý và bộ điều khiển bộ nhớ đến các bộ tăng tốc chuyên dụng cho AI và đồ họa. Các khối này, vốn chỉ chứa hàng chục nghìn transistor, giờ đây có thể chứa từ 1 triệu đến hơn 1 tỷ transistor mỗi khối. Kết quả là, các SoC này tích hợp tổng số từ 1 tỷ đến hơn 100 tỷ transistor, phản ánh sự tăng trưởng theo cấp số nhân cả về quy mô lẫn mức độ tinh vi.

Sự gia tăng số lượng khối IP và mật độ transistor đã cho phép phát triển các kiến trúc tiên tiến với nhiều cụm vi xử lý. Mỗi cụm thường chứa đến 8 lõi trong các thiết kế phổ biến, trong khi các cấu hình hiệu suất cao có thể đạt 32 lõi trở lên.

Ngày nay, các cụm vi xử lý này được tổ chức thành các mảng để cung cấp khả năng xử lý song song khổng lồ. Những thiết kế tiên tiến này tích hợp các bộ điều khiển bộ nhớ băng thông cao, các bộ tăng tốc AI chuyên dụng và các hệ thống kết nối NoC phức tạp để đảm bảo giao tiếp và khả năng mở rộng liền mạch.

Thách thức chưa từng có này có thể được quản lý bằng cách sử dụng các hệ thống kết nối NoC tiên tiến, đóng vai trò như xương sống cho việc truyền dữ liệu và giao tiếp hiệu quả trong chip. Những mạng trên chip này cho phép tích hợp mượt mà nhiều khối IP. Hơn nữa, các SoC cao cấp thường dựa vào nhiều NoC, mỗi NoC được thiết kế để phục vụ các nhiệm vụ hoặc hệ thống con cụ thể nhằm đáp ứng nhu cầu giao tiếp đa dạng trên toàn bộ chip.

Các NoC này có thể sử dụng nhiều cấu trúc liên kết khác nhau tùy theo yêu cầu ứng dụng, chẳng hạn như vòng (ring) để giao tiếp có độ trễ thấp, cây (tree) để tổ chức theo hệ thống phân cấp và lưới (mesh) để có khả năng mở rộng và linh hoạt.

Để giải quyết các thách thức về mật độ và hiệu suất, công nghệ xếp chồng 3D ngày càng được áp dụng. Các phương pháp này tích hợp nhiều lớp logic và bộ nhớ theo chiều dọc, cho phép băng thông cao hơn và độ trễ thấp hơn so với thiết kế 2D truyền thống.

Tuy nhiên, xếp chồng 3D cũng mang lại nhiều thách thức bổ sung trong thiết kế NoC, chẳng hạn như quản lý giao tiếp giữa các lớp và các ràng buộc về nhiệt, đòi hỏi các giải pháp kết nối sáng tạo hơn.

Những thách thức bổ sung

Sự phức tạp ngày càng tăng của thiết kế SoC đã tạo ra nhiều thách thức bổ sung do tốc độ phát triển nhanh của thị trường. Khi các kiến trúc trở nên phức tạp hơn, các nhà thiết kế phải đối mặt với áp lực ngày càng lớn để vượt qua những trở ngại này và áp dụng các giải pháp sáng tạo nhằm theo kịp nhu cầu của ngành.

Những thách thức chính có thể được tóm tắt như sau:

- Áp lực về thời gian đưa sản phẩm ra thị trường: Sự cạnh tranh trong thiết kế SoC hiện đại là rất lớn, và việc chậm trễ có thể dẫn đến mất doanh thu đáng kể và giảm thị phần. Các phương pháp truyền thống như cấu hình NoC thủ công tốn rất nhiều thời gian, thường kéo dài hàng tuần hoặc hàng tháng, điều này không thể chấp nhận được trong các thị trường phát triển nhanh.

- Sự khan hiếm chuyên gia: Nhu cầu về các kỹ năng chuyên môn trong thiết kế SoC đang vượt xa nguồn nhân lực sẵn có. Các nhóm kỹ sư thường bị quá tải, trong khi các chuyên gia giàu kinh nghiệm phải dành quá nhiều thời gian cho các công việc lặp đi lặp lại thay vì tập trung vào các quyết định thiết kế chiến lược.

- Việc sử dụng tài nguyên chưa tối ưu: Các phương pháp thiết kế thủ công thường dẫn đến các vấn đề như chiều dài dây dẫn quá mức, tiêu thụ điện năng cao và tắc nghẽn vật lý. Những vấn đề này ảnh hưởng đến hiệu suất tổng thể và làm tăng cả độ phức tạp trong thiết kế lẫn chi phí sản xuất.

- Công cụ thiết kế rời rạc: Các quy trình phát triển SoC bị phân mảnh do việc sử dụng các công cụ không đồng bộ trong lập kế hoạch mặt bằng, kết nối và thiết kế vật lý. Sự thiếu tích hợp giữa các giai đoạn này dẫn đến nhiều sự không hiệu quả, trì hoãn thời gian hoàn thiện thiết kế và gây khó khăn trong việc duy trì tính nhất quán trong toàn bộ quy trình.

Để giải quyết những thách thức này, cần áp dụng các phương pháp thiết kế tự động, nâng cao chuyên môn kỹ thuật và tích hợp các công cụ thiết kế để tối ưu hóa quy trình làm việc và giảm thiểu các điểm nghẽn.

Các nhà thiết kế cần giải pháp NoC thông minh hơn

Áp lực từ sự phức tạp trong thiết kế SoC thế hệ mới đang đẩy các nhóm thiết kế đến giới hạn. Một cách tiếp cận hiệu quả để quản lý những thách thức này là chia thiết kế thành các phần nhỏ hơn, dễ quản lý hơn bằng cách phân vùng thành các khối IP.

Mặc dù phương pháp này giúp đơn giản hóa các nhiệm vụ thiết kế riêng lẻ, nhưng nó cũng đặt ra một thách thức mới trong việc đảm bảo tích hợp liền mạch các khối này để tạo thành một SoC hoàn chỉnh và tối ưu. Quá trình tích hợp thường xuất hiện các vấn đề bất ngờ như giao diện không khớp, xung đột thời gian và tranh chấp tài nguyên, có thể ảnh hưởng đáng kể đến hiệu suất và làm chậm tiến độ ra mắt sản phẩm.

Nhìn chung, các giải pháp NoC thế hệ tiếp theo phải được thiết kế để đáp ứng những thách thức hiện tại đồng thời dự đoán trước những yêu cầu ngày càng tăng trong thiết kế SoC tương lai.

===

Hình ảnh đính kèm: Biểu đồ thể hiện mối quan hệ giữa sự gia tăng ngân sách transistor và việc sử dụng các khối IP. Nguồn: Arteris, dựa trên https://rb.gy/qmfcn và https://rb.gy/pgdop.

===

(*) Chú giải các từ viết tắt:

- SoC (System-on-Chip) – Hệ thống trên chip, một vi mạch tích hợp tất cả các thành phần cần thiết của một hệ thống máy tính hoặc thiết bị điện tử vào một con chip duy nhất.

- NoC (Network-on-Chip) – Mạng trên chip, một kiến trúc kết nối các thành phần khác nhau bên trong SoC nhằm tối ưu hóa hiệu suất và khả năng mở rộng.

- AI (Artificial Intelligence) – Trí tuệ nhân tạo, lĩnh vực nghiên cứu và phát triển các hệ thống có thể mô phỏng trí thông minh con người.

- HPC (High-Performance Computing) – Điện toán hiệu năng cao, đề cập đến các hệ thống máy tính có khả năng xử lý lượng dữ liệu khổng lồ với tốc độ cao.

- IP (Intellectual Property) Block – Khối IP, các mô-đun thiết kế có thể tái sử dụng trong các con chip, chẳng hạn như lõi xử lý, bộ điều khiển bộ nhớ, hoặc bộ tăng tốc AI.

- MAC (Multiply-Accumulate) – Nhân và cộng dồn, một hoạt động quan trọng trong tính toán ma trận, thường được sử dụng trong các bộ xử lý tín hiệu số và AI.

- PE (Processing Element) – Phần tử xử lý, một đơn vị tính toán nhỏ trong bộ xử lý, thường được tổ chức thành mạng lưới để xử lý song song.

- PU (Processing Unit) – Đơn vị xử lý, thành phần chính thực hiện tính toán trong một bộ xử lý hoặc bộ tăng tốc.

- NIU (Network Interface Unit) – Đơn vị giao diện mạng, phần cứng hoặc phần mềm kết nối một bộ xử lý hoặc phần tử xử lý với NoC.

Nguồn: EDN

Biên dịch bởi Admin từ Diễn đàn Vi mạch Bán dẫn và Trí tuệ Nhân tạo Việt Nam

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận