Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

Thước Đo Đánh Giá Độ Phức Tạp trong Thiết Kế VLSI: Gate Count, Transistor Count, Instance Count và Kích Thước Die

Trong thiết kế mạch tích hợp quy mô lớn (VLSI), các yếu tố Gate count (số lượng cổng logic), Transistor count (số lượng transistor), Instance count (số lượng khối mạch) và Die size (kích thước chip) là những thước đo quan trọng, được sử dụng thường xuyên để đánh giá độ phức tạp của thiết kế. Hiểu rõ các thước đo này giúp kỹ sư nắm bắt độ phức tạp của chip và tối ưu hóa phần cứng để hỗ trợ các phần mềm phức tạp.

1. Transistor Count là gì?

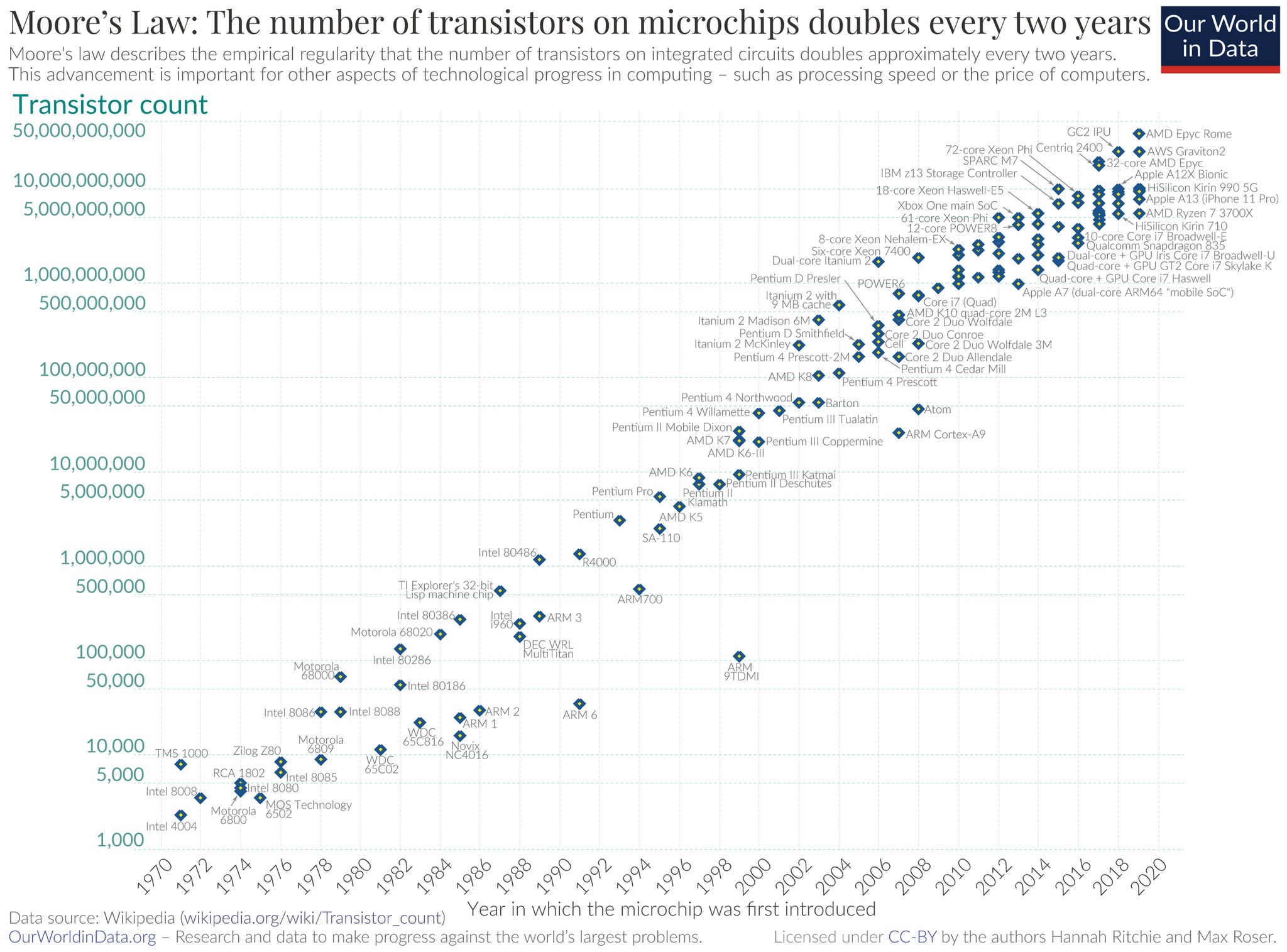

Transistor count là tổng số lượng transistor trong một thiết bị. Đây là một thước đo quan trọng vì nó phản ánh mức độ phức tạp của mạch. Ví dụ, một cổng logic NAND 2 đầu vào sẽ bao gồm 4 transistor ở cấp độ MOSFET. Điều này có liên quan mật thiết đến Định luật Moore, quy định rằng số lượng transistor trên một vi mạch sẽ tăng gấp đôi mỗi hai năm, làm gia tăng "độ phức tạp thiết kế" theo cấp số nhân qua từng năm.

2. Chip Area (Die Size) là gì?

Die size hay kích thước chip là thước đo cho biết kích thước vật lý của chip sau khi chế tạo, thường đo bằng đơn vị mm hoặc μm. Một chip có diện tích nhỏ hơn sẽ giúp chế tạo được nhiều chip hơn trên một wafer, giảm chi phí sản xuất và tăng tỷ lệ thành công. Vì vậy, việc tối ưu kích thước chip để đáp ứng phần mềm phức tạp là điều vô cùng quan trọng.

3. Gate Count là gì?

Gate count là số lượng cổng logic NAND 2 cần thiết để thể hiện toàn bộ thiết kế hoặc một module con của chip. Với một số lượng logic cụ thể (NOT, AND, OR, NOR, XOR, XNOR), các cổng này có thể chuyển đổi về số lượng tương ứng của cổng NAND. Ví dụ, một cổng NOT tương đương với một NAND, AND là hai NAND, và OR là ba NAND. Công thức tính cơ bản như sau:

- Diện tích vật lý của một cổng NAND:

dc_shell > get_attribute [get_lib_cells $your_library/your_cell_name] area. - Diện tích vật lý của thiết kế:

dc_shell > report_reference. - Tính toán Gate count: (2) / (1).

4. Instance Count là gì?

Instance count là tổng số lượng các khối mạch trong một thiết kế, bao gồm các cell trong thư viện và các thành phần hard IP (các khối logic cứng). Ví dụ, nếu thiết kế của bạn có một bộ nhớ SRAM, một CPU hard IP, và mười cổng NAND, thì Instance count sẽ là 12.

Kết luận

Nhìn chung, khi mức độ phức tạp của thiết kế chip tăng lên để đáp ứng phần mềm phức tạp, các công cụ thiết kế điện tử (EDA) sẽ yêu cầu thời gian xử lý dài hơn và các thuật toán tối ưu hóa trở nên khó khăn hơn.

Nguồn: Blog Naver

Biên dịch bởi Admin từ iCdemy.com - Đào tạo thiết kế vi mạch chuyên sâu

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận