Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

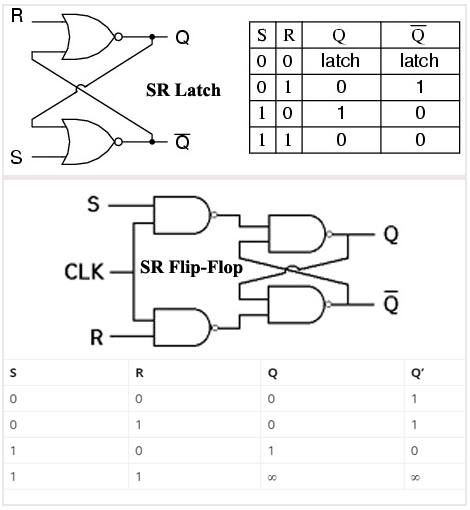

So sánh ưu nhược điểm của thiết kế dựa trên latch và thiết kế dựa trên flip-flop

Trong thiết kế mạch số, cả latch và flip-flop đều được dùng để lưu trữ thông tin trạng thái, nhưng chúng có các đặc điểm và ứng dụng khác nhau. Dưới đây là so sánh về ưu và nhược điểm của chúng:

Thiết kế dựa trên Latch

Ưu điểm:

- Đơn giản: Latch có thiết kế đơn giản hơn và có thể được triển khai với ít transistor hơn so với flip-flop.

- Tiêu thụ điện năng thấp: Do latch có thể ở trạng thái "transparent" (thụ động khi không được kích hoạt), nó có thể tiêu thụ ít năng lượng hơn trong một số trường hợp.

- Tốc độ: Latch có thể hoạt động nhanh hơn flip-flop vì chúng có thể bắt giữ dữ liệu ngay khi đầu vào thay đổi, với điều kiện là latch đang được kích hoạt.

Nhược điểm:

- Vấn đề thời gian: Latch nhạy theo mức tín hiệu (level-sensitive), nghĩa là chúng có thể thay đổi trạng thái bất kỳ lúc nào khi tín hiệu cho phép đang hoạt động. Điều này có thể gây ra các vấn đề về thời gian và nhiễu nếu không được kiểm soát cẩn thận.

- Phức tạp trong phân tích thời gian: Do tính chất "transparent," việc đảm bảo thời gian chính xác trong thiết kế đồng bộ có thể trở nên khó khăn hơn vì latch có thể gây ra các tình trạng tranh chấp.

- Ít dự đoán được: Trạng thái có thể thay đổi bất kỳ lúc nào khi latch được kích hoạt, làm cho chúng ít dự đoán được trong thiết kế đồng bộ.

Thiết kế dựa trên Flip-Flop

Ưu điểm:

- Nhạy theo biên: Flip-flop nhạy theo biên (edge-triggered), tức là chúng chỉ thay đổi trạng thái vào những thời điểm cụ thể (biên lên hoặc xuống của xung nhịp). Điều này giúp chúng dễ dự đoán hơn và dễ phân tích thời gian hơn.

- Giảm nguy cơ nhiễu: Do flip-flop chỉ lấy mẫu đầu vào tại các biên của xung nhịp, chúng ít bị ảnh hưởng bởi nhiễu gây ra bởi sự thay đổi tín hiệu đầu vào trong chu kỳ xung nhịp.

- Thiết kế đồng bộ: Flip-flop phù hợp hơn với các thiết kế đồng bộ, nơi mà mọi thay đổi trạng thái xảy ra tại các biên xung nhịp xác định, giúp đơn giản hóa phân tích thời gian và thiết kế.

Nhược điểm:

- Phức tạp hơn và chiếm diện tích lớn hơn: Flip-flop thường cần nhiều transistor hơn latch, dẫn đến kích thước mạch lớn hơn và có thể tiêu thụ nhiều điện năng hơn trong quá trình hoạt động.

- Hoạt động chậm hơn: Do đặc tính nhạy theo biên, flip-flop có thể gây ra độ trễ, khiến chúng có thể chậm hơn so với latch trong một số ứng dụng.

- Tiêu thụ điện năng: Flip-flop có thể tiêu thụ nhiều năng lượng hơn trong quá trình hoạt động do thiết kế phức tạp hơn và yêu cầu tín hiệu xung nhịp.

Tóm lại, việc chọn lựa giữa thiết kế dựa trên latch và thiết kế dựa trên flip-flop thường phụ thuộc vào các yêu cầu cụ thể của ứng dụng, chẳng hạn như tốc độ, tiêu thụ điện năng và độ phức tạp của phân tích thời gian. Latch có thể được ưu tiên trong các ứng dụng yêu cầu tiết kiệm điện năng hoặc tốc độ cao, nơi sự đơn giản trong thiết kế là quan trọng, trong khi flip-flop thường được sử dụng trong các mạch số đồng bộ nơi tính dự đoán và toàn vẹn thời gian là ưu tiên hàng đầu.

Nguồn: Admin từ iCdemy.com - Đào tạo thiết kế vi mạch chuyên sâu

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận