Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

Series Thiết kế vi mạch số sử dụng Verilog và System Verilog (Phần 2)

Thiết kế với các phần tử nguyên thủy (Primitives)

Các toán tử nguyên thủy (primitive operators) có thể được khởi tạo bao nhiêu lần và kết hợp theo bất kỳ cách nào để tạo ra một thiết kế số bất kỳ. Tuy nhiên, để tạo một thiết kế Verilog, cần có một số phần khai báo phụ trợ. Tất cả các mô tả mạch trong Verilog đều phải được đặt trong một cấu trúc gọi là “module”.

Một module Verilog hoàn chỉnh suy diễn (inferring) một mạch bộ chọn 2:1 (multiplexor) cùng với sơ đồ nguyên lý tương ứng được minh họa trong Hình 2.1 và 2.2. Một thiết kế Verilog thường được lưu trong một tệp có cùng tên với module, với phần mở rộng là .v. Các tệp viết bằng SystemVerilog sử dụng phần mở rộng .sv. Mặc dù không vi phạm cú pháp khi không tuân thủ quy ước này — ví dụ như lưu một bộ đếm (counter) trong một tệp tên là decoder.v — nhưng kiểu đặt tên gây nhầm lẫn như vậy sẽ không được chấp nhận trong môi trường làm việc chuyên nghiệp.

Hình 2.1: Một module Verilog hoàn chỉnh biểu diễn bộ chọn 2:1

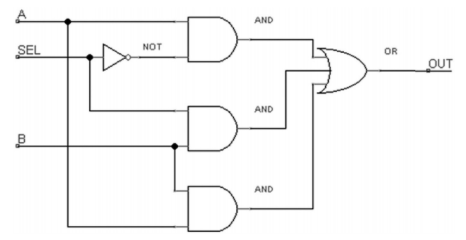

Hình 2.2: Sơ đồ nguyên lý của bộ chọn 2:1 được mô tả trong Hình 2.1

Module multiplexor có chứa chỉ thị thời gian (timescale directive), cho biết rằng mọi độ trễ trong module sẽ được tính theo đơn vị 1 nanosecond, và đơn vị thời gian nhỏ nhất mà trình mô phỏng theo dõi mà không làm tròn cũng là 1 nanosecond. Tuy nhiên, vì module này không chứa bất kỳ độ trễ nào, nên chỉ thị timescale trong trường hợp này không có tác dụng thực tế.

Sau dòng chỉ thị timescale, từ khóa module xuất hiện. Theo sau đó là tên của module và trong dấu ngoặc đơn là các cổng (ports) của module. Các cổng trong Verilog tương tự như các chân input, output và bidirectional (hai chiều) trên một thiết bị vật lý.

Mỗi cổng phải được chỉ rõ hướng (direction) của nó. Các tùy chọn gồm: input, output, và inout (hai chiều). Module này được viết theo phong cách truyền thống của Verilog. SystemVerilog cho phép viết gọn hơn bằng cách khai báo hướng của các cổng ngay trong danh sách cổng, như minh họa trong Hình 2.3. Trong Hình 2.3, mỗi primitive có thêm tên thể hiện (instance name) tùy chọn. Hiệu suất của các mô hình multiplexor trong Hình 2.1 và 2.3 là giống nhau.

Hình 2.3: Module bộ chọn viết bằng SystemVerilog

Sau phần khai báo hướng cổng, Hình 2.1 có thêm các khai báo dây nội bộ (internal wires) dùng để kết nối giữa các thể hiện. Mặc định, trình biên dịch Verilog coi các biến chưa khai báo là dây đơn bit (single-bit wire), vì vậy không nhất thiết phải khai báo nếu chỉ dùng mặc định. Tuy nhiên, có thể thay đổi kiểu biến mặc định hoặc yêu cầu tất cả các biến phải được khai báo rõ ràng. Thực hành tốt trong thiết kế là nên khai báo tất cả biến trước khi sử dụng.

Sau phần khai báo dây nội bộ là các dòng khởi tạo các primitive. Mỗi module luôn kết thúc bằng từ khóa endmodule.

Ngay cả khi chỉ làm việc với các phần tử nguyên thủy, việc chỉnh sửa và bảo trì thiết kế bằng Verilog vẫn rất dễ dàng. Giả sử bạn muốn thay đổi multiplexor để thêm một cổng AND thứ ba — nhằm ngăn chặn hiện tượng nhiễu khi chuyển mạch (glitch) xuất hiện ở đầu ra, như minh họa trong Hình 2.4. Nếu tạo nguyên mẫu bằng phần cứng, bạn sẽ cần thay thế linh kiện và đi dây lại. Nhưng với Verilog, thay đổi đó chỉ đơn thuần là việc chỉnh sửa vài dòng mã. Mã SystemVerilog cho phiên bản multiplexor đã được sửa đổi được trình bày ở Hình 2.5. Lưu ý là không cần thay thế cổng OR, chỉ cần thêm một ngõ vào mới vào danh sách cổng là đủ.

Hình 2.4: Bộ chọn 2:1 với cổng logic nhằm loại bỏ nhiễu tại đầu ra

Hình 2.5: Mã Verilog cho bộ chọn 2:1 loại bỏ nhiễu

Trong các ví dụ này, nhiều tín hiệu nội bộ kiểu wire đã được khai báo. Các đầu ra cũng được khai báo kiểu wire. Wire là một trong các kiểu biến trong Verilog. Verilog hỗ trợ một số kiểu biến hướng phần cứng mà bạn sẽ không thấy trong các ngôn ngữ lập trình thông thường. Các kiểu biến hữu ích khác sẽ được giới thiệu trong các chương sau.

Khi khai báo biến mới, mỗi biến phải có một tên duy nhất. Verilog phân biệt chữ hoa và chữ thường (case-sensitive), áp dụng cho cả biến và từ khóa. Một số ví dụ về khai báo biến wire hợp lệ, không hợp lệ, và được khuyến nghị được trình bày trong Hình 2.6. Dù Verilog phân biệt chữ hoa chữ thường, nhưng không phải công cụ tự động thiết kế nào cũng làm như vậy. Vì vậy, việc khai báo hai biến độc lập là A và a như trong Hình 2.6 tuy hợp lệ, nhưng có thể dẫn đến việc hai dây bị nối nhầm với nhau trong quá trình phát triển mạch. Nhiều nhà thiết kế sử dụng biến viết thường như trong ví dụ gần cuối, nhưng chính sách viết hoa nhất quán cho tên biến giúp mã dễ hiểu và dễ bảo trì hơn.

Hình 2.6: Các khai báo dây wire hợp lệ và không hợp lệ

Verilog tuân theo quy ước của các ngôn ngữ lập trình thông thường là cho phép chú thích (comment) ở bất kỳ đâu trong mã nguồn. Chú thích một dòng bắt đầu bằng dấu hai gạch chéo //. Chú thích nhiều dòng bắt đầu bằng /* và kết thúc bằng */. Một ví dụ về chú thích nhiều dòng được thể hiện trong Hình 2.7.

Hình 2.7: Chú thích nhiều dòng trong Verilog

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận