Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

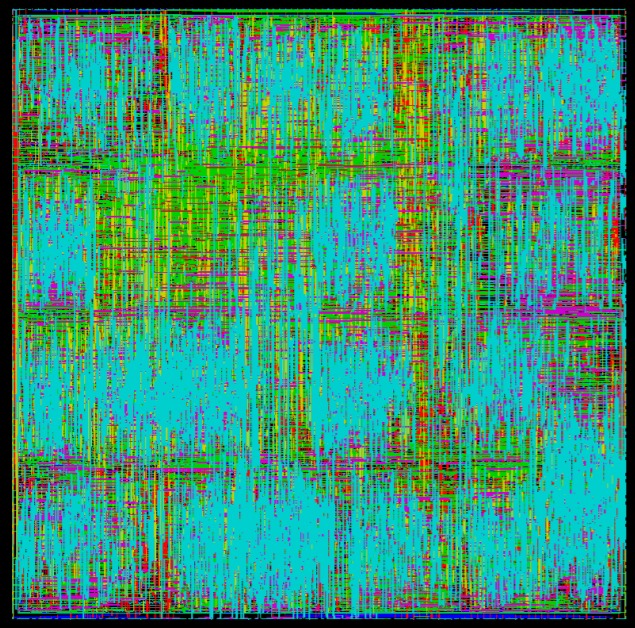

Place and Route

Place and route là một bước quan trọng trong quy trình thiết kế ASIC, đóng vai trò như người lập bản đồ và xây dựng trong “bản đồ silicon”, xác định nơi đặt các thành phần và cách chúng kết nối với nhau, đồng thời đáp ứng các yêu cầu kỹ thuật nghiêm ngặt. Vai trò của nó rất quan trọng; nếu không có các thực hành hiệu quả ở đây, những thiết kế chip sáng tạo nhất có thể không đạt hiệu suất như mong muốn.

Trong hướng dẫn toàn diện này, chúng ta sẽ tìm hiểu về độ phức tạp của place and route, khám phá từng lớp từ những khái niệm cơ bản đến các thách thức mà nhà thiết kế đối mặt. Chúng ta sẽ xem xét kỹ lưỡng về cấu trúc thiết kế, các chỉ số hiệu suất, và trang bị kiến thức về các công cụ EDA tiên tiến, thúc đẩy tương lai của thiết kế chip. Hãy cùng bắt đầu một hành trình vi mô qua các giai đoạn quan trọng và các chiến lược sáng tạo của place and route.

Place and Route là gì?

Place and route là một giai đoạn quan trọng trong quá trình tự động hóa thiết kế điện tử (EDA) cho các mạch tích hợp (IC) và bảng mạch in (PCB). Giai đoạn này diễn ra sau khi tạo ra sơ đồ mạch – nơi các thành phần điện tử được kết nối dựa trên chức năng mong muốn. Trong place and route, có hai bước chính: đầu tiên là đặt các thành phần điện tử lên chip hoặc PCB, sau đó là định tuyến các kết nối vật lý giữa chúng.

Định nghĩa và Mục đích

Quá trình place (sắp xếp) nhằm xác định vị trí tối ưu cho từng thành phần trên tấm silicon hoặc PCB, thường với các mục tiêu như giảm thiểu độ trễ, tiết kiệm không gian và giảm tiêu thụ năng lượng. Có nhiều kỹ thuật khác nhau để đạt được sắp xếp lý tưởng, xem xét kích thước, công suất và yêu cầu tản nhiệt của thành phần, cũng như độ phức tạp tổng thể của thiết kế.

Routing (định tuyến) được thực hiện sau khi sắp xếp và tập trung vào việc tạo kết nối điện giữa từng thành phần bằng dây hoặc đường dẫn kim loại. Định tuyến phải giải quyết nhiều ràng buộc và tiêu chí thiết kế như tránh nhiễu tín hiệu, đáp ứng yêu cầu thời gian và đảm bảo phân phối điện năng khắp thiết kế. Các công cụ định tuyến tiên tiến thường sử dụng các thuật toán phức tạp để điều hướng qua các thách thức định tuyến, đặc biệt trong các quy trình tiên tiến với mật độ kết nối cao.

Tầm quan trọng trong quy trình thiết kế

Place and route có vai trò rất quan trọng trong quy trình thiết kế, vì nó ảnh hưởng trực tiếp đến hiệu suất, tiêu thụ năng lượng và kích thước của sản phẩm cuối cùng. Đạt được thiết kế closure nhanh hơn – hoàn thiện thiết kế trong các thông số về thời gian và các yêu cầu khác – có thể tạo ra lợi thế cạnh tranh. Những sai lầm trong place and route có thể dẫn đến việc closure bị kéo dài, yêu cầu nhiều lần lặp và có thể làm tăng chi phí thiết kế.

Giai đoạn này cũng rất quan trọng trong việc đáp ứng các yêu cầu về thời gian để đảm bảo chip hoạt động đúng ở tốc độ nguồn xung nhịp mong muốn. Thêm vào đó, do sự liên kết chặt chẽ giữa việc sắp xếp và định tuyến, quy trình có thể tác động lớn đến khả năng mở rộng thiết kế đến các quy trình tiên tiến với các yêu cầu về quy tắc thiết kế nghiêm ngặt.

Một quy trình place and route được tối ưu hóa có thể dẫn đến một thiết kế đáp ứng các tiêu chí về tốc độ, năng lượng và diện tích (SPA), cho phép thiết kế mạch ở cấp cao đạt được các mục tiêu hiệu suất dự kiến. Hơn nữa, với sự phức tạp ngày càng tăng của các chip hiện đại, bao gồm thiết kế CPU, thiết kế analog và thiết kế bộ nhớ, các thách thức trong place and route có thể được quản lý một cách thực tiễn thông qua các chiến lược thiết kế như thiết kế phân cấp, thiết kế cong, và tối ưu hóa cho nhiều kiểu lắp ráp chip khác nhau.

Các khái niệm cơ bản

Các khái niệm cơ bản của place and route xoay quanh một số ý tưởng cốt lõi: sắp xếp vật lý các thành phần (placement), thiết lập các kết nối giữa chúng (routing), và quản lý độ phức tạp của thiết kế thông qua các cách tiếp cận phân cấp. Hiểu rõ các khái niệm này có thể góp phần vào thiết kế PCB hiệu quả và rút ngắn thời gian closure.

- Placement (Sắp xếp): Đây là quá trình bố trí các thành phần một cách hợp lý trên chip hoặc PCB. Mỗi thành phần được đặt sao cho thỏa mãn các tiêu chí như hiệu suất, hiệu quả năng lượng và sử dụng không gian. Sắp xếp tối ưu là rất quan trọng để giảm thiểu độ trễ tín hiệu và bảo tồn không gian quý giá trên silicon.

- Routing (Định tuyến): Sau khi các thành phần được sắp xếp, định tuyến thiết lập các kết nối điện giữa chúng bằng dây hoặc đường dẫn kim loại. Định tuyến hiệu quả đảm bảo rằng mạch cuối cùng đạt được tất cả các chỉ số hiệu suất mà không có vấn đề về nhiễu hoặc tính toàn vẹn tín hiệu.

- Yêu cầu về thời gian: Đáp ứng yêu cầu thời gian là cần thiết để hệ thống hoạt động ở tốc độ mong muốn, đồng bộ với nguồn xung nhịp. Điều quan trọng là phải đảm bảo nhu cầu đồng bộ hóa giữa các thành phần mạch khác nhau để tránh các vi phạm về thiết lập và giữ thời gian.

- Phân phối điện năng: Không chỉ logic và thời gian là quan trọng, mà còn phải duy trì một hệ thống phân phối điện năng mạnh mẽ. Truyền tải điện năng an toàn và hiệu quả đến tất cả các thành phần là điều cơ bản, đòi hỏi lập kế hoạch cẩn thận trong các giai đoạn sắp xếp và định tuyến.

- Các quy trình: Khi công nghệ tiến bộ, ngành công nghiệp bán dẫn chuyển sang các quy trình nhỏ hơn. Mỗi lần giảm kích thước nút quy trình thường mang đến các thách thức thiết kế tăng cao, đặc biệt là trong mật độ kết nối mà các công cụ place and route phải điều hướng.

Việc nắm vững các khái niệm cơ bản này có thể giúp các nhà thiết kế cải thiện đáng kể khả năng phát triển thiết kế lý tưởng đáp ứng các tiêu chí thiết kế định trước với ít lần lặp hơn.

Thiết kế phân cấp

Trong lĩnh vực thiết kế điện tử rộng lớn, khái niệm về thiết kế phân cấp là một chiến lược mạnh mẽ giúp tổ chức độ phức tạp của các phần tử và kết nối của mạch theo cách dễ quản lý. Thiết kế phân cấp chia nhỏ mạch thành các khối hoặc khối con, cho phép các nhà thiết kế tập trung vào các phần nhỏ hơn, dễ quản lý hơn trước khi tích hợp chúng vào sản phẩm cuối cùng. Cách tiếp cận theo mô-đun này không chỉ đơn giản hóa nhiệm vụ thiết kế mà còn cho phép phát triển song song trên các phần khác nhau của thiết kế, đẩy nhanh đáng kể quá trình tổng thể.

Trong lĩnh vực thiết kế điện tử rộng lớn, khái niệm về thiết kế phân cấp là một chiến lược mạnh mẽ giúp tổ chức độ phức tạp của các phần tử và kết nối của mạch theo cách dễ quản lý. Thiết kế phân cấp chia nhỏ mạch thành các khối hoặc khối con, cho phép các nhà thiết kế tập trung vào các phần nhỏ hơn, dễ quản lý hơn trước khi tích hợp chúng vào sản phẩm cuối cùng. Cách tiếp cận theo mô-đun này không chỉ đơn giản hóa nhiệm vụ thiết kế mà còn cho phép phát triển song song trên các phần khác nhau của thiết kế, đẩy nhanh đáng kể quá trình tổng thể.

Lợi ích chính của phương pháp thiết kế phân cấp bao gồm:

• Dễ dàng gỡ lỗi: Bằng cách chia thiết kế thành các khối chức năng, việc xác định và xử lý sự cố trở nên dễ dàng hơn. • Tái sử dụng thiết kế: Thiết kế phân cấp cho phép khả năng tái sử dụng các khối đã có trong các thiết kế mới, từ đó tiết kiệm thời gian và tài nguyên. • Cải thiện tổ chức: Điều này cho phép các nhóm làm việc đồng thời trên các phần khác nhau của thiết kế, tối ưu hóa việc sử dụng lực lượng lao động và giảm thời gian hoàn thiện thiết kế.

Áp dụng thiết kế phân cấp là một yếu tố quan trọng trong việc quản lý độ phức tạp của thiết kế và các thách thức mở rộng gặp phải với tiến bộ công nghệ.

Tái sử dụng thiết kế

Nguyên tắc tái sử dụng thiết kế đã trở thành một phần không thể thiếu trong thiết kế IC và PCB. Bằng cách tái sử dụng các thành phần hoặc khối thiết kế hiện có đã được xác minh và tối ưu hóa, các nhà thiết kế có thể giảm đáng kể thời gian và chi phí thiết kế.

Nguyên tắc tái sử dụng thiết kế đã trở thành một phần không thể thiếu trong thiết kế IC và PCB. Bằng cách tái sử dụng các thành phần hoặc khối thiết kế hiện có đã được xác minh và tối ưu hóa, các nhà thiết kế có thể giảm đáng kể thời gian và chi phí thiết kế.

Lợi ích của việc tái sử dụng thiết kế bao gồm:

• Tính nhất quán: Thúc đẩy việc sử dụng các khối xây dựng đã được thử nghiệm, đảm bảo chất lượng nhất quán. • Hiệu quả: Tái sử dụng các thành phần giúp rút ngắn thời gian hoàn thiện thiết kế vì phần lớn công việc đã được thực hiện và xác minh trong các dự án trước. • Phân bổ tài nguyên: Kỹ sư có thể dành nhiều nguồn lực hơn cho các khía cạnh sáng tạo của thiết kế, thay vì tạo lại từ đầu trong mỗi chu kỳ thiết kế mới.

Để tận dụng tối đa việc tái sử dụng thiết kế, các tổ chức thường duy trì các thư viện tệp thiết kế — một kho lưu trữ được lựa chọn cẩn thận về các thành phần, hệ thống con và tiêu chí thiết kế mà các nhóm thiết kế có thể khai thác.

Các chỉ số thiết kế

Các chỉ số thiết kế là các phép đo định lượng giúp đánh giá chất lượng và hiệu quả của quy trình thiết kế và sản phẩm cuối cùng. Các chỉ số phổ biến bao gồm diện tích, tốc độ, tiêu thụ năng lượng và số lần lặp lại cần thiết để đạt được thiết kế hoàn chỉnh. Ngoài ra, các chỉ số như tỷ lệ sản phẩm đạt chuẩn, điểm số khả năng sản xuất và chi phí trên mỗi đơn vị cũng đóng vai trò quan trọng trong việc đánh giá tính khả thi kinh tế của một thiết kế.

Các chỉ số thiết kế là các phép đo định lượng giúp đánh giá chất lượng và hiệu quả của quy trình thiết kế và sản phẩm cuối cùng. Các chỉ số phổ biến bao gồm diện tích, tốc độ, tiêu thụ năng lượng và số lần lặp lại cần thiết để đạt được thiết kế hoàn chỉnh. Ngoài ra, các chỉ số như tỷ lệ sản phẩm đạt chuẩn, điểm số khả năng sản xuất và chi phí trên mỗi đơn vị cũng đóng vai trò quan trọng trong việc đánh giá tính khả thi kinh tế của một thiết kế.

Các chỉ số thường định hướng quá trình thiết kế bằng cách cung cấp các mục tiêu rõ ràng và cho phép so sánh khách quan các cách tiếp cận thiết kế hoặc công cụ khác nhau. Đo lường và phân tích chính xác các chỉ số này có thể dẫn đến tiến độ thiết kế dự đoán được, sản xuất hiệu quả về chi phí và sản phẩm chất lượng cao.

Độ phức tạp của thiết kế

Các thách thức do độ phức tạp của thiết kế mang lại là không thể xem nhẹ. Khi nhu cầu của người tiêu dùng và ngành công nghiệp thúc đẩy các sản phẩm có chức năng và hiệu suất cao hơn, đóng gói trong kích thước ngày càng nhỏ gọn, độ phức tạp của thiết kế cũng tăng lên tương ứng. Độ phức tạp của thiết kế biểu hiện ở mật độ kết nối cao, yêu cầu về năng lượng và tản nhiệt chặt chẽ hơn, và sự tích hợp của các hệ thống dị hợp như mạch tương tự, số và hỗn hợp tín hiệu trên một con chip.

Các thách thức do độ phức tạp của thiết kế mang lại là không thể xem nhẹ. Khi nhu cầu của người tiêu dùng và ngành công nghiệp thúc đẩy các sản phẩm có chức năng và hiệu suất cao hơn, đóng gói trong kích thước ngày càng nhỏ gọn, độ phức tạp của thiết kế cũng tăng lên tương ứng. Độ phức tạp của thiết kế biểu hiện ở mật độ kết nối cao, yêu cầu về năng lượng và tản nhiệt chặt chẽ hơn, và sự tích hợp của các hệ thống dị hợp như mạch tương tự, số và hỗn hợp tín hiệu trên một con chip.

Để đối phó với độ phức tạp này, các nhà thiết kế sử dụng một loạt các công cụ EDA tinh vi, sử dụng các thuật toán tiên tiến cho bố trí và định tuyến có thể quản lý hàng nghìn thành phần và kết nối. Thông qua các phương pháp thiết kế phân cấp và tái sử dụng thiết kế, kết hợp với việc sử dụng nhiều kỹ thuật khác nhau, các thách thức phức tạp của các node tiến trình tiên tiến và tích hợp mạch phức tạp có thể được điều hướng một cách hiệu quả.

Quy trình Place and Route

Tổng quan về quy trình

Quy trình place and route (P&R) là một giai đoạn quan trọng trong quy trình tự động hóa thiết kế điện tử (EDA), quyết định hiệu suất và chức năng cuối cùng của các mạch tích hợp (IC) và bảng mạch in (PCB). Quy trình phức tạp này bao gồm một chuỗi các bước chuyển đổi thiết kế mạch cấp cao thành một sản phẩm vật lý sẵn sàng cho sản xuất. Các bước quan trọng bao gồm thiết kế cấp cao, tổng hợp logic, tạo netlist, phân tích thời gian, triển khai vật lý và các hoạt động chính là bố trí và định tuyến. Mỗi bước tuân theo một hướng dẫn nghiêm ngặt để đáp ứng các ràng buộc điện và vật lý, đảm bảo rằng mạch đáp ứng tất cả các yêu cầu hoạt động.

Quy trình place and route (P&R) là một giai đoạn quan trọng trong quy trình tự động hóa thiết kế điện tử (EDA), quyết định hiệu suất và chức năng cuối cùng của các mạch tích hợp (IC) và bảng mạch in (PCB). Quy trình phức tạp này bao gồm một chuỗi các bước chuyển đổi thiết kế mạch cấp cao thành một sản phẩm vật lý sẵn sàng cho sản xuất. Các bước quan trọng bao gồm thiết kế cấp cao, tổng hợp logic, tạo netlist, phân tích thời gian, triển khai vật lý và các hoạt động chính là bố trí và định tuyến. Mỗi bước tuân theo một hướng dẫn nghiêm ngặt để đáp ứng các ràng buộc điện và vật lý, đảm bảo rằng mạch đáp ứng tất cả các yêu cầu hoạt động.

Thiết kế mạch cấp cao

Trong hành trình từ ý tưởng đến sản phẩm hữu hình, thiết kế mạch cấp cao đóng vai trò là bản thiết kế. Các kỹ sư xác định các yêu cầu chức năng, xác định kiến trúc và chọn các thành phần và mô hình kết nối phù hợp. Họ đưa ra các quyết định cơ bản để phân phối xung nhịp, tính toàn vẹn tín hiệu và quản lý năng lượng. Giai đoạn thiết kế cấp cao này đặt nền tảng cho P&R thành công bằng cách phù hợp với các cân nhắc thiết kế phức tạp ở các node tiến trình tiên tiến và phong cách thiết kế lắp ráp phức tạp.

Trong hành trình từ ý tưởng đến sản phẩm hữu hình, thiết kế mạch cấp cao đóng vai trò là bản thiết kế. Các kỹ sư xác định các yêu cầu chức năng, xác định kiến trúc và chọn các thành phần và mô hình kết nối phù hợp. Họ đưa ra các quyết định cơ bản để phân phối xung nhịp, tính toàn vẹn tín hiệu và quản lý năng lượng. Giai đoạn thiết kế cấp cao này đặt nền tảng cho P&R thành công bằng cách phù hợp với các cân nhắc thiết kế phức tạp ở các node tiến trình tiên tiến và phong cách thiết kế lắp ráp phức tạp.

Tổng hợp logic

Sau thiết kế cấp cao, tổng hợp logic chuyển đổi mô tả mạch trừu tượng thành các biểu diễn cấp cổng. Giai đoạn này sử dụng các thuật toán tinh vi để tối ưu hóa mạch về diện tích, thời gian và năng lượng đồng thời tuân thủ các tiêu chí thiết kế xác định. Logic được tối ưu hóa kết quả đóng vai trò là cầu nối giữa chức năng lý thuyết của mạch và triển khai thực tế, đảm bảo rằng các mục tiêu thiết kế ban đầu phù hợp với thực tế sản xuất.

Sau thiết kế cấp cao, tổng hợp logic chuyển đổi mô tả mạch trừu tượng thành các biểu diễn cấp cổng. Giai đoạn này sử dụng các thuật toán tinh vi để tối ưu hóa mạch về diện tích, thời gian và năng lượng đồng thời tuân thủ các tiêu chí thiết kế xác định. Logic được tối ưu hóa kết quả đóng vai trò là cầu nối giữa chức năng lý thuyết của mạch và triển khai thực tế, đảm bảo rằng các mục tiêu thiết kế ban đầu phù hợp với thực tế sản xuất.

Tạo Netlist

Tạo netlist là một bước chuyển đổi biến logic tổng hợp thành danh sách các thành phần điện tử (như transistor, điện trở, tụ điện) và kết nối chính xác của chúng, gọi là netlist. Netlist đóng vai trò là cơ sở nền tảng cho các giai đoạn thiết kế vật lý tiếp theo, là nguồn quan trọng để đảm bảo các mục tiêu về thời gian, năng lượng và diện tích khả thi ở cấp độ triển khai.

Tạo netlist là một bước chuyển đổi biến logic tổng hợp thành danh sách các thành phần điện tử (như transistor, điện trở, tụ điện) và kết nối chính xác của chúng, gọi là netlist. Netlist đóng vai trò là cơ sở nền tảng cho các giai đoạn thiết kế vật lý tiếp theo, là nguồn quan trọng để đảm bảo các mục tiêu về thời gian, năng lượng và diện tích khả thi ở cấp độ triển khai.

Phân tích thời gian

Trước khi đi vào bố trí vật lý, phân tích thời gian đánh giá mạch một cách nghiêm ngặt dựa trên các yêu cầu thời gian của nó, đảm bảo rằng các tín hiệu truyền qua trong khoảng thời gian chấp nhận được, tránh các tình huống chạy đua hoặc vi phạm thời gian thiết lập và giữ. Các công cụ phân tích thời gian mô phỏng hành vi của mạch trong nhiều kịch bản hoạt động khác nhau, cung cấp thông tin điều chỉnh thiết kế cần thiết để giải quyết các vấn đề thời gian.

Trước khi đi vào bố trí vật lý, phân tích thời gian đánh giá mạch một cách nghiêm ngặt dựa trên các yêu cầu thời gian của nó, đảm bảo rằng các tín hiệu truyền qua trong khoảng thời gian chấp nhận được, tránh các tình huống chạy đua hoặc vi phạm thời gian thiết lập và giữ. Các công cụ phân tích thời gian mô phỏng hành vi của mạch trong nhiều kịch bản hoạt động khác nhau, cung cấp thông tin điều chỉnh thiết kế cần thiết để giải quyết các vấn đề thời gian.

Triển khai vật lý

Triển khai vật lý chuyển đổi netlist và dữ liệu thời gian thành cấu hình không gian của các phần tử mạch trong không gian của silicon. Nó bao gồm việc bố trí các thành phần cá nhân một cách cẩn thận và định tuyến kết nối chính xác, với mục tiêu giảm thiểu độ trễ và tối đa hóa hiệu quả của mạch. Các thuật toán phức tạp xem xét các thách thức độc đáo của node tiến trình mong muốn, quản lý tích hợp mật độ cao đồng thời tuân thủ các yêu cầu chặt chẽ về phân phối nhiệt và năng lượng.

Triển khai vật lý chuyển đổi netlist và dữ liệu thời gian thành cấu hình không gian của các phần tử mạch trong không gian của silicon. Nó bao gồm việc bố trí các thành phần cá nhân một cách cẩn thận và định tuyến kết nối chính xác, với mục tiêu giảm thiểu độ trễ và tối đa hóa hiệu quả của mạch. Các thuật toán phức tạp xem xét các thách thức độc đáo của node tiến trình mong muốn, quản lý tích hợp mật độ cao đồng thời tuân thủ các yêu cầu chặt chẽ về phân phối nhiệt và năng lượng.

Bố trí và Định vị

Bố trí và định vị bao gồm việc sắp xếp chiến lược các thành phần trên IC hoặc PCB, cân bằng giữa việc sử dụng không gian tối ưu với các yêu cầu về tính toàn vẹn chức năng và tín hiệu. Đảm bảo rằng phân phối năng lượng được tích hợp liền mạch, các công cụ thiết kế điều hướng một cách thành thạo các yêu cầu cạnh tranh về việc giảm thiểu diện tích đồng thời tối ưu hóa hiệu suất và khả năng sản xuất. Quy trình bao gồm nhiều lần lặp lại, với các đánh giá thiết kế đảm bảo tuân thủ các tiêu chí thiết kế trong suốt giai đoạn này.

Bố trí và định vị bao gồm việc sắp xếp chiến lược các thành phần trên IC hoặc PCB, cân bằng giữa việc sử dụng không gian tối ưu với các yêu cầu về tính toàn vẹn chức năng và tín hiệu. Đảm bảo rằng phân phối năng lượng được tích hợp liền mạch, các công cụ thiết kế điều hướng một cách thành thạo các yêu cầu cạnh tranh về việc giảm thiểu diện tích đồng thời tối ưu hóa hiệu suất và khả năng sản xuất. Quy trình bao gồm nhiều lần lặp lại, với các đánh giá thiết kế đảm bảo tuân thủ các tiêu chí thiết kế trong suốt giai đoạn này.

Định tuyến

Giai đoạn cuối trong quy trình P&R, định tuyến, thiết lập mạng lưới phức tạp các đường dẫn điện kết nối các thành phần đã bố trí. Điều này bao gồm các thuật toán có độ phức tạp cao để tạo ra các đường dẫn ít nhiễu, giảm thiểu thất thoát tín hiệu và tránh các đường giao nhau. Định tuyến cuối cùng ảnh hưởng đến hiệu suất, độ ổn định và khả năng sản xuất của mạch, và với việc hoàn thành nó, thiết kế P&R cuối cùng được đánh giá để đảm bảo rằng tất cả các yêu cầu kỹ thuật đã được đáp ứng, chuẩn bị cho sản xuất.

Giai đoạn cuối trong quy trình P&R, định tuyến, thiết lập mạng lưới phức tạp các đường dẫn điện kết nối các thành phần đã bố trí. Điều này bao gồm các thuật toán có độ phức tạp cao để tạo ra các đường dẫn ít nhiễu, giảm thiểu thất thoát tín hiệu và tránh các đường giao nhau. Định tuyến cuối cùng ảnh hưởng đến hiệu suất, độ ổn định và khả năng sản xuất của mạch, và với việc hoàn thành nó, thiết kế P&R cuối cùng được đánh giá để đảm bảo rằng tất cả các yêu cầu kỹ thuật đã được đáp ứng, chuẩn bị cho sản xuất.

Nguồn: Anysilicon

Biên dịch bởi Admin từ iCdemy.com - Đào tạo thiết kế vi mạch chuyên sâu

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận