Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

Phân tích công suất trong công nghệ 7nm (Phần 1)

Bài viết này thảo luận về phân tích công suất của một con chip mạng phức tạp ở công nghệ 7nm. Khi các hệ thống trên chip (SoC) thế hệ mới tiến tới tương lai, kích thước chip giảm đi cùng lúc với việc tăng số lượng transistor chuyển mạch nhằm đáp ứng nhu cầu chức năng tốt hơn. Phân tích thiết kế đúng cách giúp giảm thiểu rủi ro, rút ngắn thời gian ra thị trường và cung cấp chất lượng thiết kế tốt nhất về công suất, hiệu năng, diện tích và độ tin cậy.

Hiện tượng sụt áp xảy ra tại các lưới dây kim loại ngay trước các chân cấp nguồn của các cell chuẩn, thường được gọi là sụt áp IR. Nó phát sinh do điện trở gặp phải trên dây kim loại và dòng điện chạy qua chúng.

Quản lý hiệu quả sụt áp IR là vô cùng quan trọng trong thiết kế chip vì nó ảnh hưởng lớn đến nhiều yếu tố của hiệu suất chip. Dưới đây là cách sụt áp IR ảnh hưởng đến các yếu tố khác nhau:

- Công suất: Sụt áp IR ảnh hưởng trực tiếp đến việc cung cấp công suất cho các cell bên trong chip. Khi dây kim loại có điện trở cao, nó dẫn đến sụt áp lớn hơn, làm giảm điện áp cung cấp cho các cell. Điều này có thể gây ra lỗi chức năng, tăng tiêu thụ điện năng và giảm hiệu năng do điện áp cung cấp giảm.

- Hiệu năng: Sụt áp IR có tác động đến thời gian và hiệu suất tổng thể của chip. Nếu điện áp của các cell giảm đáng kể do sụt áp IR lớn, có thể dẫn đến tốc độ chuyển mạch chậm hơn và thời gian lan truyền tín hiệu tăng, ảnh hưởng đến tần số hoạt động và thời gian đáp ứng của chip.

- Diện tích: Để giảm thiểu sụt áp IR, các nhà thiết kế thường phải thêm nhiều lớp kim loại hoặc làm rộng dây, điều này có thể chiếm thêm diện tích trên chip, hạn chế không gian cho các thành phần khác.

- Độ tin cậy: Sụt áp IR quá mức có thể gây ra vấn đề về độ tin cậy. Điện áp không đủ ở các cell có thể dẫn đến lỗi chức năng hoặc thậm chí hư hỏng chip vĩnh viễn, biểu hiện qua vi phạm thời gian, vấn đề về tính toàn vẹn tín hiệu, và tăng khả năng chịu nhiễu.

Để giải quyết các vấn đề này và kiểm soát sụt áp IR, các nhà thiết kế chip áp dụng một số kỹ thuật, bao gồm:

- Thiết kế Mạng phân phối nguồn (PDN): Tối ưu hóa bố cục PDN như định vị cẩn thận các đường điện và đất, thêm tụ bù (De-Caps) ở các khu vực có mật độ cao, và triển khai cấu trúc lưới điện hiệu quả để giảm thiểu sụt áp IR.

- Clock và Power gating: Tắt nguồn cho các phần hoặc phần không hoạt động của chip có thể giảm tiêu thụ điện năng và sụt áp IR.

- Phân tích tính toàn vẹn tín hiệu: Thực hiện phân tích kỹ lưỡng để xác định các đường dẫn và khu vực quan trọng có dòng điện cao giúp tối ưu hóa lộ trình và giảm thiểu ảnh hưởng của sụt áp IR.

- Lập kế hoạch mặt bằng theo dòng điện: Cân nhắc đến yêu cầu cấp nguồn và giảm thiểu các đoạn dây dài, hỗ trợ giảm sụt áp IR.

- Phân tích và tối ưu hóa sụt áp: Xem xét các vùng có mật độ cao trong thiết kế với các cell có khả năng điều khiển mạnh. Thực hiện điều chỉnh hợp lý trong luồng PNR thông qua việc trải cell, áp dụng các vùng hạn chế cho các cell đặt gần nhau hoặc có mật độ chân cao trong khu vực đó. Bố trí khoảng cách hợp lý giữa các cell đồng hồ cũng giúp tránh các vấn đề sụt áp IR tiềm ẩn.

Ở các nút công nghệ tiên tiến, cùng với kích thước transistor, kích thước dây kim loại cũng được thu nhỏ, dẫn đến điện trở kim loại tăng, trở thành yếu tố chi phối ở nút công nghệ thấp. Điều này gây ra sụt áp IR và hiện tượng di chuyển electron, cả hai có thể dẫn đến lỗi chức năng của thiết kế.

Tại các nút công nghệ thấp, mật độ dòng điện động tăng do các transistor đặt gần nhau hơn, gây ra nhiệt kẹt giữa các răng. Đồng thời, dòng điện rò tăng ở các công nghệ thấp, góp phần vào sự di chuyển của kim loại.

Tổng quan về IR tĩnh, IR động và Điện di

Mạng phân phối nguồn gặp phải hiện tượng sụt áp, được gọi là IR tĩnh, khi không có sự chuyển đổi hoặc thay đổi tín hiệu đầu vào. Mất áp trong mạng cấp nguồn do các tín hiệu đầu vào chuyển đổi liên tục được gọi là IR động. Vấn đề chính của IR là các khối logic chiếm ưu thế, nơi có thể cần giảm bớt tài nguyên định tuyến PG (Power-Ground).

Điện di là sự dịch chuyển nguyên tử do dòng điện đi qua vật liệu. Khi mật độ dòng điện đủ lớn, nhiệt sinh ra trong vật liệu sẽ gây tách và dịch chuyển các nguyên tử, tạo ra các "khoảng trống" và "cặn bã". Cặn bã có thể phát triển và tạo ngắn mạch trong khi các khoảng trống có thể mở rộng và gây đứt mạch, dẫn đến hở mạch.

Các thách thức gặp phải trong thiết kế:

Để đảm bảo dữ liệu chính xác và cung cấp cái nhìn rõ ràng hơn về kết quả phân tích, đã có sự điều chỉnh và thay đổi trong quy trình IR. Dưới đây là một số thay đổi có thể thực hiện, và chúng ta sẽ thảo luận về cả điều chỉnh quy trình và phương pháp thiết kế vật lý để khắc phục IR.

Trường hợp 1: Tính toán MIM Cap trong phân tích IR

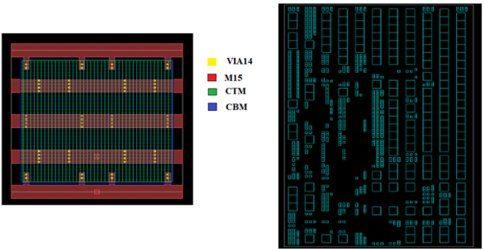

MIMCAP (Metal-Insulator-Metal Capacitor), một tụ điện với các tấm song song, được tạo thành từ hai lớp kim loại. Có một lớp cách điện mỏng giữa các lớp kim loại trên (CTM) và dưới (CBM) của tụ điện. Các lớp MIM này bao gồm các vật liệu như Al, hợp kim AlCu, TiN, Ti, TaN và Ta. Các lớp cách điện được làm từ silicon oxide hoặc silicon nitride.

MIMCAP được dùng để cung cấp dung lượng tách sóng, giúp giảm nhiễu nguồn và giảm thiểu các ảnh hưởng tiêu cực lên mạng nguồn. Chúng được đặt giữa các lớp kim loại 14 và 15 trong công nghệ 7nm.

Để công cụ phân tích IR xem xét hiệu ứng của MIMCAP, thông tin về các lớp CTM và CBM phải có trong tệp DEF, do đó, MIMCAP là một trường hợp đặc biệt yêu cầu tạo tệp mô hình IR để xem xét hiệu ứng của nó.

Sử dụng công cụ redhawk-sc (gds2rh), chúng ta cần tạo LEF và DEF chi tiết đã trích xuất để tính đến tác động của MIMCAP.

Công cụ IR (gds2rh) cần các tệp đầu vào sau để trích xuất LEF và DEF của MIMCAP:

- MIMCAP GDS

- Tệp bản đồ lớp công nghệ của Apache

- MIMCAP LEF

Thông tin LEF và DEF được trích xuất thành đầu ra, sau đó sẽ được công cụ IR sử dụng làm đầu vào để tính đến tác động của MIMCAP.

P/s: hình 1, thông tin từng lớp MIMCAP đơn lẻ và cấu trúc MIMCAP cho các cấp khối.

===

(*) Chú giải các từ viết tắt:

- SoC (System on a Chip): Hệ thống trên một chip

- IR (Internal Resistance): Điện trở nội tại

- PDN (Power Distribution Network): Mạng phân phối nguồn

- De-Caps (Decoupling Capacitors): Tụ bù

- PNR (Place and Route): Quá trình đặt và định tuyến

- PG (Power-Ground): Nguồn - Đất

- MIMCAP (Metal-Insulator-Metal Capacitor): Tụ điện kim loại-cách điện-kim loại

- CTM (Capacitor Top Metal): Kim loại trên của tụ điện

- CBM (Capacitor Bottom Metal): Kim loại dưới của tụ điện

- DEF (Design Exchange Format): Định dạng trao đổi thiết kế

- LEF (Library Exchange Format): Định dạng trao đổi thư viện

- GDS (Graphic Data System): Hệ thống dữ liệu đồ họa

- PG Routing (Power-Ground Routing): Định tuyến nguồn - đất

Còn tiếp...

Nguồn: Design Reuse

Biên dịch bởi Admin từ iCdemy.com - Đào tạo thiết kế vi mạch chuyên sâu

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận