Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

Phân tích thời gian tĩnh (Static Timing Analysis - STA)

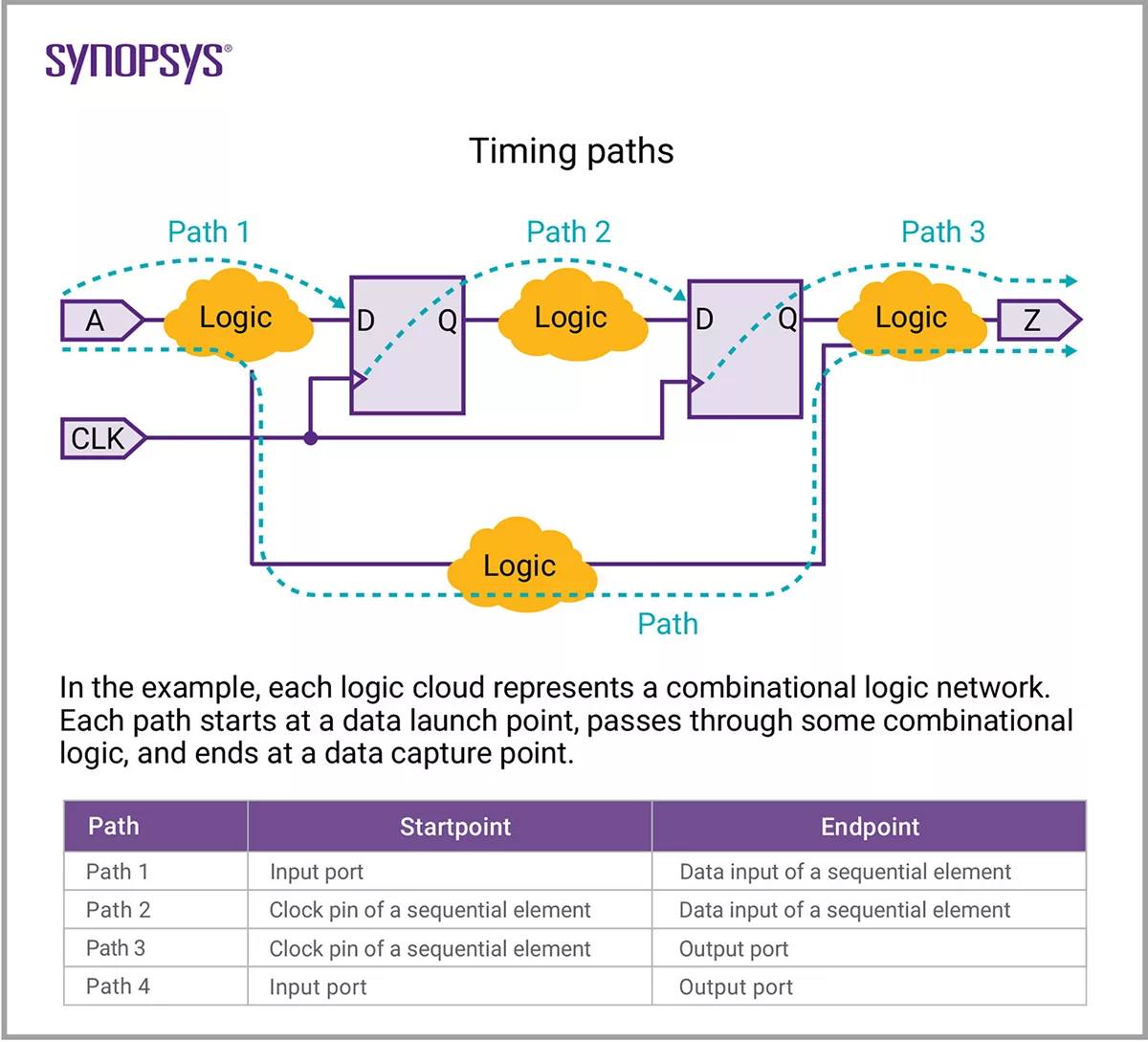

Phân tích thời gian tĩnh (STA) là một phương pháp xác nhận hiệu suất thời gian của một thiết kế bằng cách kiểm tra tất cả các đường dẫn có thể để phát hiện các vi phạm về thời gian. STA chia nhỏ một thiết kế thành các đường dẫn thời gian, tính toán độ trễ truyền tín hiệu dọc theo mỗi đường dẫn và kiểm tra các vi phạm về các ràng buộc thời gian trong thiết kế cũng như tại giao diện đầu vào/đầu ra.

Một phương pháp khác để thực hiện phân tích thời gian là mô phỏng động, phương pháp này xác định hành vi đầy đủ của mạch đối với một tập hợp vector kích thích đầu vào nhất định. So với mô phỏng động, phân tích thời gian tĩnh nhanh hơn rất nhiều vì không cần phải mô phỏng hoạt động logic của mạch. STA cũng toàn diện hơn vì kiểm tra tất cả các đường dẫn thời gian, không chỉ các điều kiện logic được kích hoạt bởi một tập hợp các vector kiểm tra. Tuy nhiên, STA chỉ có thể kiểm tra thời gian, không thể kiểm tra chức năng của thiết kế mạch.

STA Hoạt Động Như Thế Nào?

Khi thực hiện phân tích thời gian, STA đầu tiên chia nhỏ thiết kế thành các đường dẫn thời gian. Mỗi đường dẫn thời gian bao gồm các yếu tố sau:

- Điểm khởi đầu (Startpoint): Là điểm bắt đầu của một đường dẫn thời gian nơi dữ liệu được khởi tạo bởi một cạnh xung nhịp hoặc nơi dữ liệu phải có sẵn tại một thời điểm cụ thể. Mỗi điểm khởi đầu phải là một cổng đầu vào hoặc một chân xung nhịp của thanh ghi.

- Mạng logic tổ hợp (Combinational logic network): Các phần tử không có bộ nhớ hoặc trạng thái bên trong. Logic tổ hợp có thể chứa các phần tử AND, OR, XOR và inverter, nhưng không thể chứa flip-flop, latch, thanh ghi hoặc RAM.

- Điểm kết thúc (Endpoint): Là điểm cuối của một đường dẫn thời gian nơi dữ liệu được lấy bởi một cạnh xung nhịp hoặc nơi dữ liệu phải có sẵn tại một thời điểm cụ thể. Mỗi điểm kết thúc phải là một chân đầu vào dữ liệu của thanh ghi hoặc một cổng đầu ra.

Mây logic tổ hợp có thể chứa nhiều đường dẫn và STA sử dụng đường dẫn dài nhất để tính toán độ trễ tối đa và đường dẫn ngắn nhất để tính toán độ trễ tối thiểu.

STA cũng xem xét các loại đường dẫn sau cho phân tích thời gian:

- Đường dẫn xung nhịp (Clock path): Một đường từ cổng đầu vào xung nhịp hoặc chân của một cell, qua một hoặc nhiều bộ đệm hoặc inverter, đến chân xung nhịp của phần tử tuần tự; được sử dụng để kiểm tra thiết lập và giữ dữ liệu.

- Đường dẫn chặn xung nhịp (Clock-gating path): Một đường từ cổng đầu vào đến phần tử chặn xung nhịp; được sử dụng để kiểm tra thiết lập và giữ dữ liệu trong chặn xung nhịp.

- Đường dẫn không đồng bộ (Asynchronous path): Một đường từ cổng đầu vào đến chân đặt hoặc xóa không đồng bộ của phần tử tuần tự; được sử dụng để kiểm tra phục hồi và loại bỏ.

Sau khi chia nhỏ một thiết kế thành tập hợp các đường dẫn thời gian, công cụ STA tính toán độ trễ dọc theo mỗi đường dẫn. Tổng độ trễ của một đường dẫn là tổng của tất cả các độ trễ của cell và net trong đường dẫn.

- Độ trễ cell (Cell delay) là lượng độ trễ từ đầu vào đến đầu ra của một cổng logic trong đường dẫn. Khi không có thông tin độ trễ chú thích ngược từ tệp SDF, công cụ sẽ tính toán độ trễ cell từ các bảng độ trễ được cung cấp trong thư viện logic cho cell.

Thông thường, một bảng độ trễ liệt kê lượng độ trễ là một hàm của một hoặc nhiều biến, chẳng hạn như thời gian chuyển tiếp đầu vào và điện dung tải đầu ra. Từ các mục trong bảng này, công cụ tính toán độ trễ của từng cell.

- Độ trễ net (Net delay) là lượng độ trễ từ đầu ra của một cell đến đầu vào của cell tiếp theo trong đường dẫn thời gian. Độ trễ này được gây ra bởi điện dung ký sinh của kết nối giữa hai cell, kết hợp với điện trở của net và khả năng chịu tải hạn chế của cell dẫn net.

STA sau đó kiểm tra các vi phạm của các ràng buộc thời gian, chẳng hạn như ràng buộc thiết lập và giữ:

- Ràng buộc thiết lập (Setup constraint) chỉ định thời gian cần thiết để dữ liệu có sẵn tại đầu vào của một thiết bị tuần tự trước cạnh xung nhịp nắm dữ liệu trong thiết bị. Ràng buộc này thực thi một độ trễ tối đa trên đường dữ liệu so với cạnh xung nhịp.

- Ràng buộc giữ (Hold constraint) chỉ định thời gian cần thiết để dữ liệu ổn định tại đầu vào của thiết bị tuần tự sau cạnh xung nhịp nắm dữ liệu trong thiết bị. Ràng buộc này thực thi một độ trễ tối thiểu trên đường dữ liệu so với cạnh xung nhịp.

Nếu một số đường dẫn không có ý định hoạt động theo hành vi thiết lập và giữ mặc định mà công cụ STA giả định, bạn cần chỉ định các đường dẫn đó là các ngoại lệ thời gian. Nếu không, công cụ có thể báo cáo không chính xác các đường dẫn đó là có vi phạm thời gian.

Công cụ STA có thể cho phép chỉ định các loại ngoại lệ sau:

- Đường dẫn giả (False path): Một đường dẫn không bao giờ được kích hoạt do cấu hình logic, trình tự dữ liệu mong đợi hoặc chế độ hoạt động.

- Đường dẫn đa chu kỳ (Multicycle path): Một đường dẫn được thiết kế để mất nhiều hơn một chu kỳ xung nhịp từ lúc khởi tạo đến lúc lấy.

- Đường dẫn độ trễ tối thiểu hoặc tối đa (Minimum or maximum delay path): Một đường dẫn phải đáp ứng ràng buộc độ trễ mà bạn chỉ định rõ ràng dưới dạng giá trị thời gian.

Nguồn: Synopsys

Biên dịch bởi Admin từ iCdemy.com - Đào tạo thiết kế vi mạch chuyên sâu

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận