Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

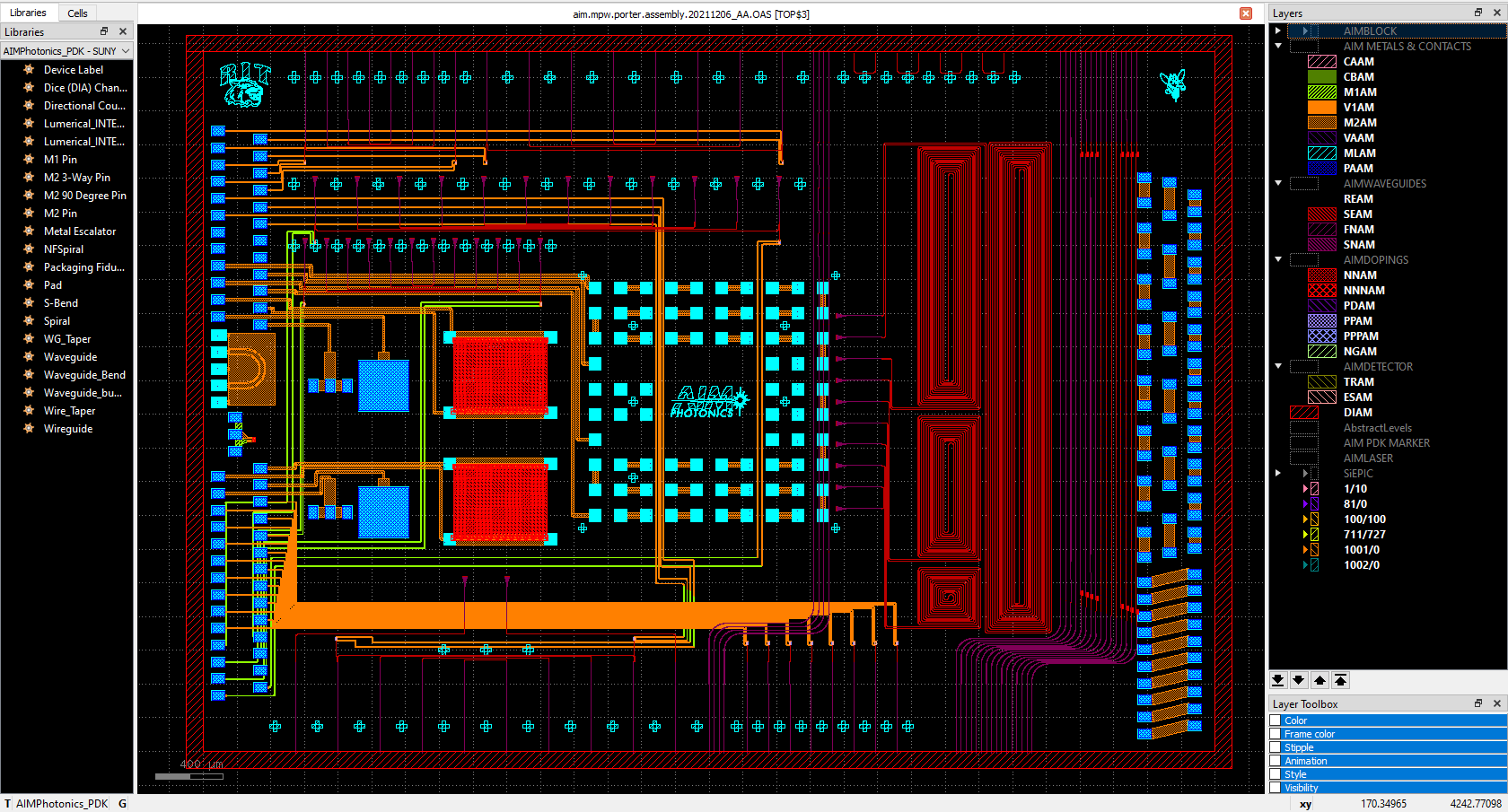

PDK – Bộ công cụ khai mở thế giới silicon

Bạn vừa nhận một task thiết kế chip trên tiến trình 65nm.

RTL đã có, schematic bạn vẽ ổn, layout bạn cũng đã từng làm. Nhưng câu hỏi lập

tức xuất hiện: điện áp nguồn bao nhiêu là đúng? Có bao nhiêu lớp kim loại

để route? Chiều rộng dây poly thế nào là hợp lý? Và transistor thì nên có kích

thước bao nhiêu để cân bằng hiệu suất và diện tích?

Bạn không thể trả lời những câu hỏi này một cách chính xác – nếu

thiếu PDK.

1.

PDK là gì?

PDK – Process Design Kit – là bộ công cụ được cung cấp bởi các

hãng foundry (như TSMC, Intel, SkyWater, Samsung, GlobalFoundries...)

giúp các kỹ sư thiết kế mạch có thể tạo ra layout, mô phỏng và tối ưu mạch

sao cho phù hợp với khả năng chế tạo thực tế của nhà máy.

PDK là chiếc cầu nối giữa ý tưởng thiết kế và sản phẩm thực tế

trên silicon. Không có PDK, bạn không thể đảm bảo rằng: layout bạn vẽ có thể

được sản xuất, mạch bạn mô phỏng có chính xác, hay cell bạn dựng có thể tái sử

dụng trong các khối phức tạp hơn.

2.

Một bộ PDK gồm

những gì?

Một PDK đầy đủ sẽ bao gồm nhiều thành phần, được chia làm 2

nhóm chính:

1. Mô hình điện và công cụ mô phỏng

- SPICE

model: mô hình transistor (NMOS, PMOS) ở các điều kiện công nghệ

khác nhau, dùng để mô phỏng delay, công suất, mức nhiễu…

- Corner

models: bao gồm các điều kiện góc như TT (typical), SS

(slow-slow), FF (fast-fast) giúp bạn đánh giá mạch trong tình huống xấu

nhất, tốt nhất hoặc trung bình.

- Parasitic

extraction rules: định nghĩa cách tính toán điện trở, điện

dung ký sinh từ layout – rất quan trọng với tốc độ mạch.

2. Mô tả vật lý và công cụ kiểm tra

- DRC /

LVS rule deck: các quy tắc vật lý để kiểm tra layout hợp

lệ (DRC) và kiểm tra layout khớp với schematic (LVS).

- Layer

map và Technology file: định nghĩa các lớp vật liệu trong tiến

trình: số lớp kim loại, chức năng mỗi lớp, độ dày, khoảng cách tối thiểu,

chiều rộng tối thiểu…

- PCell

(Parameter Cell): cell tham số hoá cho layout – ví dụ: một

transistor có thể thay đổi chiều dài, chiều rộng mà vẫn đúng chuẩn.

- Symbol

và layout template: thư viện cell để bạn xây dựng schematic

nhanh chóng, từ các inverter, NAND, đến SRAM, flip-flop.

- Script

& Utility: công cụ sẵn có để tự động hoá việc kiểm

tra DRC, LVS, chạy mô phỏng, tạo netlist hoặc build standard cell.

3.

PDK hoạt động

ra sao trong thực tế thiết kế?

Giả sử bạn vẽ một inverter đơn giản.

- Khi vẽ

schematic: bạn kéo NMOS, PMOS từ thư viện symbol có trong PDK.

- Khi dựng

layout: bạn dùng cell layout có sẵn, vẽ dây route, sau đó kiểm tra bằng

DRC/LVS rules.

- Khi mô

phỏng: bạn sử dụng SPICE model từ PDK để chạy mô phỏng timing, power.

- Khi

extract parasitic: bạn dùng file rule có trong PDK để lấy netlist chứa ký

sinh RC, rồi chạy mô phỏng hậu layout (post-layout simulation).

=> Mọi bước trong quy trình đều xoay quanh PDK. Nếu PDK

lỗi, thiếu dữ liệu, hoặc outdated, bạn có thể tape-out một con chip không chạy

được.

4.

Ví dụ thực tế:

SkyWater 130nm vs TSMC 5nm

SkyWater 130nm:

- Là tiến

trình open-source được phát hành công khai.

- Ai cũng

có thể tải, học, vẽ mạch, chạy mô phỏng và thậm chí tape-out chip thật

với chi phí rất thấp (hàng trăm USD).

- Thích hợp

cho giáo dục, nghiên cứu, khởi nghiệp.

TSMC 5nm:

- PDK được

bảo mật nghiêm ngặt, chỉ cung cấp cho khách hàng lớn, có ký hợp đồng NDA.

- Mỗi

dòng dữ liệu trong PDK có thể trị giá hàng triệu đô vì liên quan đến

bí mật công nghệ của tiến trình hàng đầu thế giới.

- PDK ở

đây còn bao gồm cả thư viện chuẩn cell, SRAM, ESD cell, IO block, IP

analog...

=> Dù bạn làm chip học thuật hay thương mại, không có PDK –

không có chip.

5.

Bạn dùng PDK để

làm gì?

- Vẽ

schematic và layout

- Mô phỏng

mạch (pre-layout, post-layout)

- Tối ưu

transistor theo corner

- Kiểm

tra DRC, LVS, và extract parasitic

- Thiết kế

standard cell, SRAM, analog IP

- Chuẩn bị

tape-out (GDSII final)

6.

Kết luận: PDK

không chỉ là công cụ – mà là chìa khóa

Bạn có thể giỏi mô phỏng, giỏi thiết kế RTL, giỏi layout, nhưng nếu

không biết cách đọc, hiểu và khai thác PDK, bạn đang làm việc "mù

đường" trong thế giới vi mạch.

PDK là nền tảng của mọi con chip. Hiểu PDK là bước đầu tiên để làm chủ

thiết kế, và cũng là bước cuối cùng trước khi sản phẩm của bạn ra đời.

Bạn đã từng sử dụng PDK nào? SkyWater open-source? TSMC

28nm? Hay một PDK học thuật khác?

Và nếu bạn từng gặp lỗi chỉ vì một dòng rule sai trong DRC, hãy chia sẻ

– biết đâu kinh nghiệm đó giúp người khác tránh được một tape-out thất bại.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận