Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

PARASITIC EXTRACTION – KHI CON CHIP LÊN BÀN MỚI BIẾT SỰ THẬT

Bạn viết RTL, mô phỏng sạch sẽ, mọi thứ hoạt động đúng như kỳ vọng. Sau đó, bạn layout xong, chạy LVS thành công. Tín hiệu từ điểm A đến B, theo tính toán sơ bộ, lẽ ra chỉ mất khoảng 10 picosecond để truyền đi. Nhưng đến khi silicon thật ra đời, bạn phát hiện delay thực tế là… 40 picosecond. Tín hiệu bị chậm, mạch vi phạm timing, thậm chí hoạt động sai.

Chuyện gì đã xảy ra?

Đó chính là parasitic – những thành phần “kí sinh” âm thầm xuất hiện trong layout thực tế. Chúng không có trong schematic, không thấy được trong RTL hoặc waveforms, nhưng luôn tồn tại ngoài đời thật và ảnh hưởng trực tiếp đến độ trễ, độ nhiễu, độ ổn định của mạch. Nếu bạn không tính đến chúng, những con số lý tưởng của bạn… sẽ mãi chỉ là lý tưởng.

Parasitic là gì?

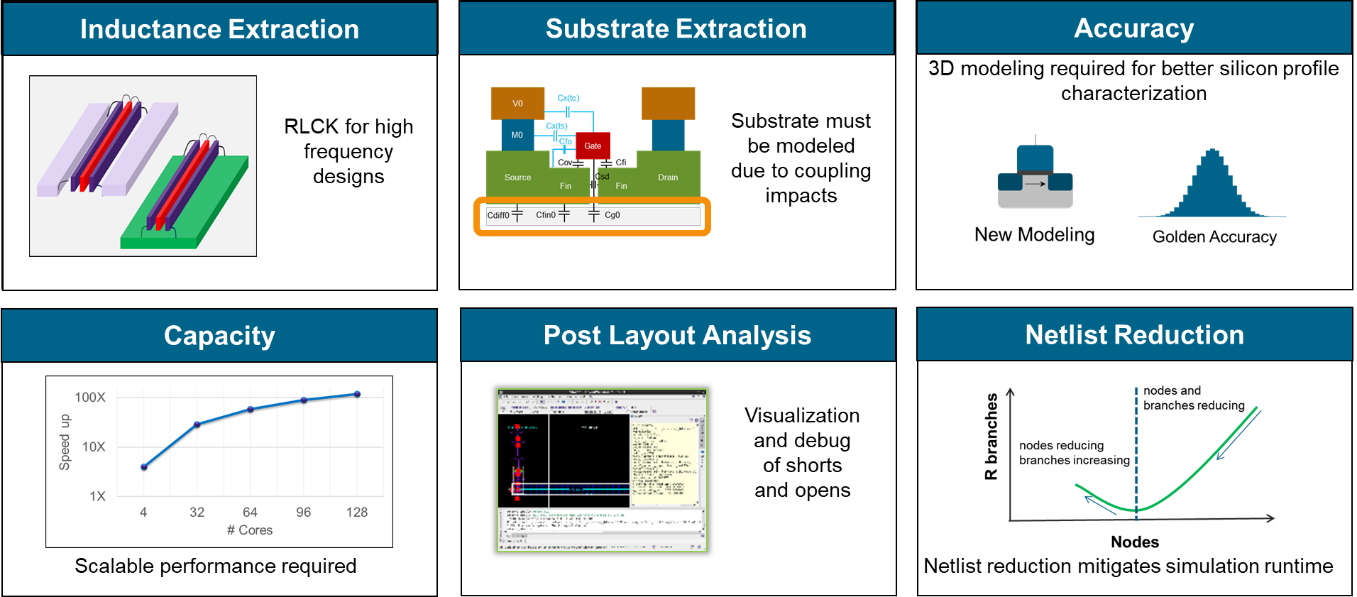

Parasitic (các thành phần kí sinh) là những điện trở (R), điện dung (C) và cảm kháng (L) không mong muốn được hình thành bởi chính layout mà bạn vẽ. Ví dụ:

-

Mỗi đoạn dây kim loại đều có điện trở nội tại, phụ thuộc vào chiều dài, bề rộng và lớp kim loại sử dụng.

-

Khoảng cách giữa hai dây gần nhau tạo nên một điện dung ký sinh.

-

Những vòng dây lớn hoặc mạch lặp có thể sinh ra cảm kháng ký sinh.

Các parasitic này là yếu tố vật lý không thể loại bỏ hoàn toàn – chỉ có thể đo lường, trích xuất và tính toán trước khi chip được sản xuất.

Parasitic Extraction là gì và dùng để làm gì?

Parasitic Extraction (PEX) là quá trình trích xuất đầy đủ các parasitic từ layout thực tế (sau khi đi dây xong) để đưa vào mô phỏng hoặc phân tích timing. Việc này giúp bạn:

-

Biết được độ trễ thực tế của từng tín hiệu trên chip

-

Phát hiện những vùng có điện trở cao, dễ gây sụt áp (IR drop)

-

Xác định tín hiệu dễ bị nhiễu hoặc cross-talk

-

Đảm bảo layout an toàn về điện áp và dòng điện

Công cụ thường dùng:

-

StarRC (Synopsys)

-

Calibre xACT (Siemens)

-

OpenRCX (open-source)

-

Output thường là các file SPEF, DSPF, SDF – được dùng trong mô phỏng hậu layout (post-layout simulation) hoặc phân tích timing tĩnh (Static Timing Analysis – STA).

Tình huống thực tế: thiết kế buffer cho mạng clock

Bạn đang thiết kế buffer để phân phối clock cho một khối mạch lớn. Trên schematic, delay từ đầu vào đến đầu ra là 8ps – mọi thứ có vẻ ổn. Nhưng khi layout hoàn tất:

-

Dây clock chạy xa

-

Fanout lớn

-

Điện dung dây tăng mạnh

Sau khi bạn trích xuất parasitic, delay thực tế tăng lên 20–30ps. Nếu bạn không đưa parasitic vào phân tích STA hoặc post-layout sim, bạn có thể vi phạm hold time, dẫn đến lỗi logic trên silicon thật.

Lúc đó, sửa lỗi không còn là sửa RTL nữa – mà là... chờ tape-out lần sau, tốn thêm hàng trăm nghìn USD.

Sau khi extract parasitic, bạn có thể làm gì?

1. Phân tích timing chính xác hơn:

Chạy lại STA với file SPEF hoặc SDF để tìm ra lỗi timing, critical path thực sự.

2. Mô phỏng post-layout:

Sử dụng netlist đã bao gồm parasitic trong HSPICE, PrimeSim, VCS để mô phỏng.

3. Phân tích cross-talk và glitch:

Xác định xem các tín hiệu có gây nhiễu lên nhau hay không, đặc biệt với clock và reset.

4. Tối ưu layout:

Sau khi biết được parasitic gây ảnh hưởng lớn, bạn có thể:

-

Đi dây ngắn hơn

-

Thêm buffer để tăng drive strength

-

Tách các net có điện dung lớn

-

Tránh chạy song song các net nhạy cảm

Kết luận: Không thể thiết kế một con chip nghiêm túc mà bỏ qua parasitic

Schematic không nói dối – nhưng cũng không nói hết sự thật.

Nếu chỉ nhìn vào RTL hoặc schematic, bạn sẽ nghĩ mạch chạy tốt. Nhưng chỉ khi trích xuất parasitic, đưa chúng vào trong mô phỏng và STA, bạn mới thực sự hiểu được mạch của mình sẽ vận hành như thế nào ngoài đời thực.

Thẻ:

ParasiticExtraction LayoutToReality ChipDesign ICVerification HocICcungICdemy thiết kế vi mạch iCdemy0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận