Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

Những thách thức đa vật lý trong thiết kế 3D IC

Những thách thức đa vật lý trong thiết kế 3D IC

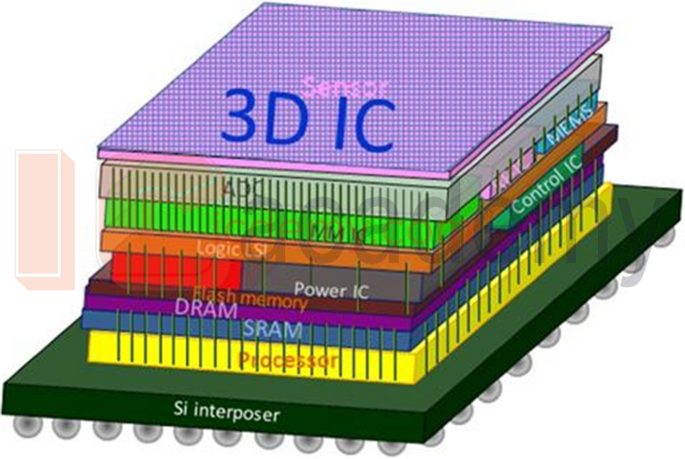

Ngành công nghiệp bán dẫn đã tích hợp ngày càng nhiều chức năng vào các không gian nhỏ hơn và hiện đang bắt đầu xây dựng theo chiều dọc. Với sự phát triển của three-dimensional integrated circuits (3D ICs), các nhà thiết kế có thể đóng gói nhiều sức mạnh xử lý và chức năng hơn vào các không gian nhỏ gọn hơn. Tuy nhiên, chiều không gian mới này cũng mang đến một loạt thách thức, bao gồm mechanical stresses và thermal effects, có ảnh hưởng trực tiếp đến hành vi điện của mạch.

Trong các thiết kế truyền thống như IC hoặc system-on-chip (SoC), những tác động này phần lớn được kiểm soát nhờ vào việc tất cả các linh kiện đều nằm trên một silicon die chung. Chỉ cần áp dụng một số quy tắc thiết kế thích hợp để giữ khoảng cách đủ lớn giữa các linh kiện, các nhà thiết kế có thể đảm bảo rằng hầu hết các tác động tiêu cực được giảm thiểu hoặc tránh được. Bằng cách trích xuất thêm một số tham số của linh kiện, các vấn đề nghiêm trọng có thể được phát hiện để xem xét lại, cho phép các mối quan ngại bổ sung được xác định trong quá trình mô phỏng hậu layout. Tuy nhiên, trong thiết kế 3D IC, những biện pháp bảo vệ này không còn khả thi nữa.

Tiềm năng và thách thức của 3D IC

Không giống như các IC truyền thống, 3D ICs xếp chồng nhiều chiplet riêng lẻ, có thể được chế tạo trên các process node khác nhau và được kết nối thông qua vertical interconnect accesses (vias) để tạo thành một gói nhỏ gọn duy nhất. Cách tiếp cận này mang lại nhiều lợi ích:

- Hiệu suất chip tốt hơn: Giảm khoảng cách giữa các thành phần giúp giảm độ trễ truyền tín hiệu, dẫn đến tốc độ xử lý nhanh hơn.

- Tăng cường chức năng chip: Nhiều chức năng có thể được tích hợp trong một gói duy nhất để tạo ra các thiết bị phức tạp và mạnh mẽ hơn.

- Tiêu thụ điện năng thấp hơn: Đường kết nối ngắn hơn có thể dẫn đến mức tiêu thụ điện năng thấp hơn so với các 2D IC truyền thống.

Tuy nhiên, không có gì là miễn phí. Quá trình chuyển đổi sang 3D ICs cũng tạo ra nhiều thách thức mới, đặc biệt là trong design verification, khi các nhà thiết kế phải đảm bảo rằng các active chiplet trong một hệ thống 3D IC sẽ hoạt động như mong đợi. Verification cho 3D ICs bao gồm việc phát hiện các vấn đề design rule checking (DRC), layout vs. schematic (LVS), xác định cross-die parasitic coupling và phân tích 3D thermal và stress.

Giải nhiệt trong 3D ICs là một bài toán phức tạp do nhiều yếu tố:

- Khoảng cách gần giữa các linh kiện dẫn đến mật độ công suất cao, gây ra lượng nhiệt lớn.

- Non-homogeneous power distribution có thể tạo ra thermal gradients, khiến các vùng khác nhau của chip có nhiệt độ khác nhau.

- Stacked thinned dies làm tăng thermal resistance, khiến việc tản nhiệt trở nên khó khăn hơn.

Do đó, việc phân tích và quản lý nhiệt mạnh mẽ là rất quan trọng trong suốt quá trình thiết kế.

Xác định ảnh hưởng điện của mechanical stresses

Nhiệt không phải là thách thức duy nhất trong 3D ICs. Mechanical stresses cũng có thể ảnh hưởng đến hiệu suất điện của chip. Các nhà thiết kế sử dụng phần mềm chuyên dụng để phân tích ảnh hưởng của tất cả các loại stress lên active chiplets.

Họ có thể tạo ra stress map bằng cách sử dụng cùng một mô hình assembly stack-up definition và thuộc tính mechanical stress của từng vật liệu trong toàn bộ cụm lắp ráp. Giống như phân tích nhiệt, các dữ liệu này có thể được chuyển xuống cấp thiết bị để mô phỏng chính xác sau khi lắp ráp.

Sự tương tác giữa mechanical stress, thermal impacts và electrical behavior

- Mechanical stresses tạo ra nhiệt.

- Thermal impacts gây ra mechanical stress.

- Cả hai đều ảnh hưởng đến hành vi điện, từ đó sinh thêm nhiệt.

Việc giảm thiểu các tác động này có thể được thực hiện thông qua quá trình lặp. Power map có thể được sử dụng để trích xuất thermal map, sau đó được chuyển để bổ sung vào stress maps. Các tác động stress và thermal có thể được chuyển vào device-level netlist để mô phỏng, cập nhật EMIR analysis, v.v.

Tuy nhiên, ngay cả khi đã kết hợp thermal và mechanical stress verification, vẫn chưa đủ. Nếu final signoff verification phát hiện vấn đề, thì đã quá muộn để thực hiện các điều chỉnh cần thiết trong quá trình lắp ráp.

Phân tích sớm và thường xuyên

Truyền thống, phân tích thermal và stress thường được thực hiện ở cấp package và system, tách biệt khỏi quá trình thiết kế IC. Tuy nhiên, đối với 3D ICs, phương pháp này không còn phù hợp nữa. Phân tích giai đoạn đầu từ khi chọn floorplan, xuyên suốt quá trình IC implementation và signoff, hiện là điều bắt buộc.

Tích hợp thực tiễn và khả năng sử dụng

Phân tích thermo-mechanical nên được tích hợp trực tiếp vào design flow, cung cấp automation tiên tiến để giúp người dùng dễ sử dụng hơn. Các tính năng như:

- Tối ưu hóa lưới nhiệt (gridding)

- Giảm độ phức tạp mô hình

- Tự động trích xuất thông số nhiệt tương đương

- Nén power maps và tạo báo cáo

Ngoài ra, một GUI trực quan giúp các nhà thiết kế dễ dàng nhận diện thermal hotspots và các loại stress khác nhau.

Giải pháp cho phân tích nhiệt và stress ở cấp die

Các nhà thiết kế có thể sử dụng chip-package thermal and stress co-design flows để thực hiện phân tích toàn diện từ giai đoạn đầu đến khi final signoff. Các đặc điểm chính của một giải pháp multiphysics analysis hiệu quả bao gồm:

- Tích hợp với IC design flow

- Độ chính xác và độ phân giải cao

- Mô phỏng tự động

- Khả năng phân tích lặp

Một số giải pháp mới tích hợp 3D solver vào các nền tảng thiết kế IC hiện có, giúp phân tích thermal và stress chính xác hơn.

Kết luận

Sự chuyển dịch sang 3D ICs mang lại một bước tiến lớn trong thiết kế bán dẫn, mở ra tiềm năng mới về hiệu suất và chức năng. Tuy nhiên, các thách thức thermo-mechanical đòi hỏi các giải pháp multiphysics analysis tiên tiến, giúp phát hiện và khắc phục sớm các vấn đề nhiệt và stress để đảm bảo sản phẩm cuối cùng đạt tiêu chuẩn về hiệu suất và độ tin cậy.

===

(*) Chú giải các từ viết tắt:

- 3D IC (Three-Dimensional Integrated Circuit): Mạch tích hợp ba chiều

- SoC (System-on-Chip): Hệ thống trên chip

- DRC (Design Rule Checking): Kiểm tra quy tắc thiết kế

- LVS (Layout vs. Schematic): So sánh sơ đồ bố cục với sơ đồ mạch

- DEF (Design Exchange Format): Định dạng trao đổi thiết kế

- ECXML (Electronics Cooling XML): Định dạng XML cho phân tích làm mát điện tử

- EMIR (Electromigration and IR drop Analysis): Phân tích di cư điện tử và sụt áp IR

Nguồn: Thời báo Điện-Điện tử

Biên dịch bởi Admin từ iCdemy.com - Đào tạo thiết kế vi mạch chuyên sâu

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận