Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

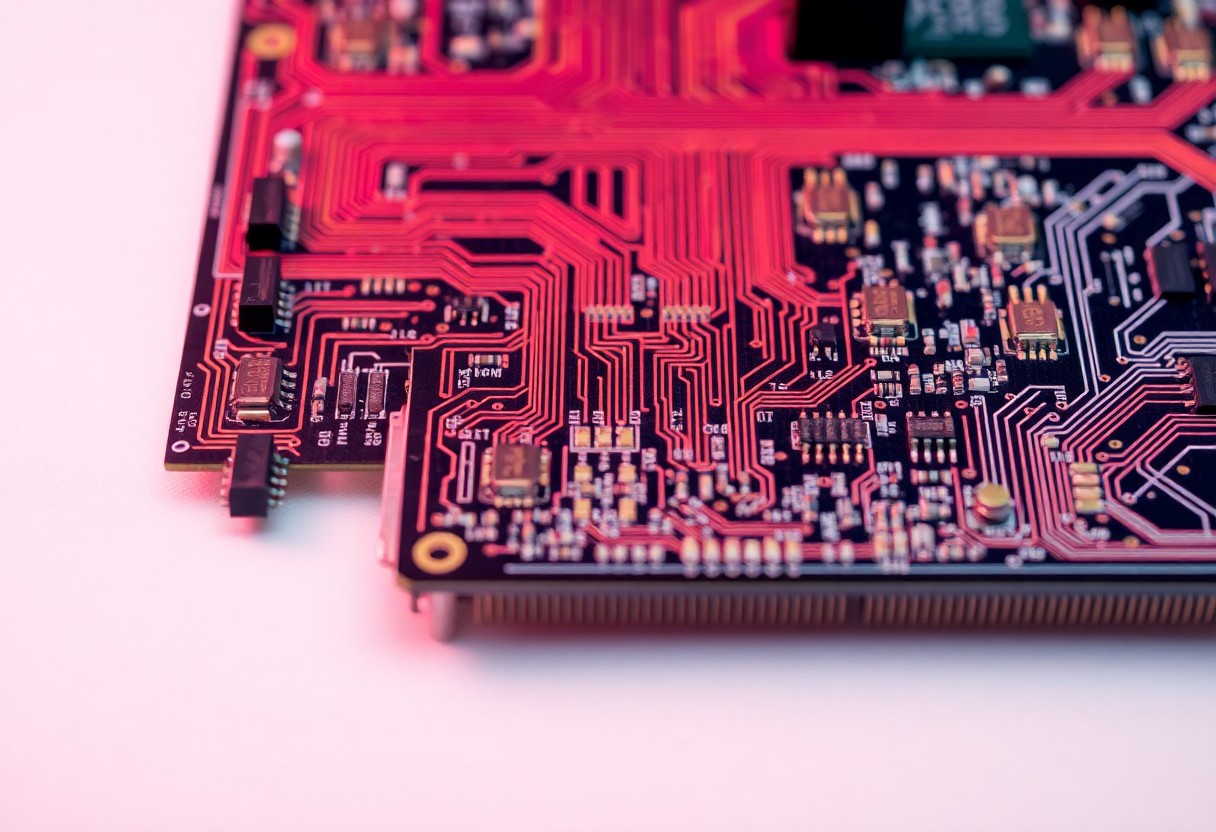

MASK – MẶT NẠ THIẾT KẾ CỦA THẾ GIỚI VI MẠCH

Bạn có từng thắc mắc: Làm thế nào để những thiết kế vi mạch phức tạp với hàng tỷ transistor lại có thể được “sao chép” chính xác đến từng nanomet trên tấm wafer silicon?

Câu trả lời nằm ở Photomask – linh hồn của quy trình Lithography.

Mỗi mask là một “bản thiết kế thu nhỏ”, định hình từng lớp transistor, contact,

via hay interconnect trong con chip của bạn. Đây là bước trung gian thiết yếu,

giúp chuyển từ thiết kế logic (trên phần mềm EDA) sang hiện thực vật lý (trên

wafer).

1.

Mask là gì?

Photomask là một tấm kính (thường làm từ thủy tinh thạch

anh) có phủ lớp hấp thụ ánh sáng kim loại – thường là chrome. Trên lớp này sẽ

được khắc các hình mẫu cực nhỏ tương ứng với từng lớp thiết kế của vi mạch.

Trong quy trình quang khắc (lithography), ánh sáng

chiếu qua mask, chỉ truyền qua những vùng trong suốt, còn các vùng phủ chrome sẽ

chặn lại. Từ đó, ánh sáng sẽ “in” các hình dạng mong muốn lên lớp photoresist

trên bề mặt wafer silicon – giống như cách ảnh âm bản hoạt động trong nhiếp ảnh

film.

Mỗi con chip hoàn chỉnh có thể cần đến 20–60 mask

khác nhau, tương ứng với hàng chục lớp chế tạo như: lớp khuếch tán (diffusion),

lớp cổng (gate), lớp kim loại (metal), lớp lỗ thông (via), lớp passivation,

v.v. Đối với các chip cao cấp sử dụng công nghệ EUV hoặc multi-patterning, số

lượng mask có thể lên đến 80 hoặc hơn.

2.

Cấu trúc của một Photomask

Một photomask hiện đại thường gồm bốn phần chính:

- Substrate

(đế): Là tấm kính thạch anh (fused silica) có độ tinh khiết cao, trong

suốt với ánh sáng cực tím, đặc biệt là DUV (193 nm) hoặc không truyền với

EUV (13.5 nm).

- Chrome

layer: Lớp kim loại mỏng phủ lên bề mặt kính, có khả năng hấp thụ hoặc

phản xạ ánh sáng để tạo vùng tối.

- Pattern:

Các vùng được khắc bỏ lớp chrome theo mẫu thiết kế. Đây là nơi ánh sáng có

thể đi qua và “in” lên wafer.

- Pellicle:

Lớp màng polymer mỏng, căng phía trên mask (cách khoảng vài mm), giúp ngăn

bụi tiếp xúc trực tiếp với bề mặt mask. Khi có bụi bám vào pellicle, bóng

đổ của nó sẽ bị mờ, không gây ảnh hưởng nghiêm trọng đến hình ảnh in ra

wafer.

3.

Các loại mask phổ biến

Binary

Mask (Mask nhị phân)

Đây là loại mask đơn giản nhất, chỉ có hai trạng thái: hoặc

cho ánh sáng đi qua (trong suốt), hoặc ngăn hoàn toàn (phủ chrome). Loại mask

này được sử dụng rộng rãi trong các quy trình DUV thông thường.

Mặc dù đơn giản, binary mask có giới hạn về độ phân giải, nhất

là khi bước sóng ánh sáng tiệm cận hoặc nhỏ hơn kích thước cần in. Do đó, các

công nghệ nâng cao đã được phát triển để cải thiện chất lượng hình ảnh.

Phase

Shift Mask (PSM)

Mask dịch pha sử dụng hiện tượng giao thoa ánh sáng để cải

thiện độ sắc nét và phân giải của hình ảnh in ra.

Có hai loại PSM chính:

- Alternating

PSM: Sử dụng các vùng tạo pha khác nhau (thường lệch 180 độ), làm tăng

độ tương phản ở biên mẫu.

- Attenuated

PSM: Dùng vật liệu bán trong suốt để ánh sáng đi qua bị suy giảm và

thay đổi pha, tạo hiệu ứng mép ảnh sắc nét hơn.

PSM giúp in được các chi tiết nhỏ hơn nhiều so với giới hạn

nhiễu xạ thông thường.

EUV Mask

EUV (Extreme Ultraviolet) mask không thể sử dụng kính thông

thường, vì ánh sáng 13.5 nm không truyền qua bất kỳ vật liệu nào. Thay vào đó,

EUV mask là một gương nhiều lớp (multilayer mirror), được thiết kế để phản

xạ ánh sáng thay vì truyền qua.

Cấu trúc EUV mask bao gồm:

- Substrate

bằng molybdenum silicon

- ~40–50

lớp vật liệu nano (Mo/Si) xếp chồng như gương Bragg

- Lớp

phủ hấp thụ (absorber layer) để tạo hình mẫu

- Pellicle

đặc biệt (hoặc không có) vì EUV rất nhạy với bụi

EUV mask cực kỳ đắt đỏ, với chi phí từ 300,000 đến 1 triệu

USD cho mỗi tấm. Việc sửa lỗi cũng phức tạp và yêu cầu phòng sạch cấp độ cao nhất.

4.

Làm sao tạo ra mask?

Việc chế tạo mask yêu cầu công nghệ chính xác tuyệt đối. Quy

trình điển hình gồm các bước:

- Viết

mask (Mask Writing): Sử dụng E-beam writer (Electron Beam

Lithography) – thiết bị dùng chùm electron để “vẽ” trực tiếp mẫu lên lớp

photoresist phủ trên mask blank. Đây là quá trình tốn thời gian vì cần viết

từng điểm một (serial).

- Khắc

(Etching): Sau khi mẫu được vẽ, phần không che chắn sẽ bị loại bỏ bằng

khắc khô hoặc khắc ướt, tạo nên các vùng truyền sáng và chặn sáng.

- Làm

sạch & phủ pellicle: Mask sau khi hoàn thiện được làm sạch siêu

âm, kiểm tra lỗi và phủ lớp pellicle để bảo vệ.

Toàn bộ quy trình có thể kéo dài vài ngày đến một tuần,

và đòi hỏi môi trường kiểm soát bụi nghiêm ngặt. Một lỗi nhỏ cũng có thể làm hỏng

toàn bộ mask hoặc gây lỗi hàng loạt trên wafer.

5.

Các thách thức kỹ thuật

- Defect-free

(Không lỗi): Chỉ một hạt bụi hoặc khuyết tật trên mask cũng có thể in

lỗi lên toàn bộ wafer → gây thiệt hại hàng trăm ngàn USD.

- Mask

3D effect: Do mask không phẳng hoàn hảo, hiệu ứng ba chiều có thể làm

méo hình ảnh. Cần sử dụng OPC (Optical Proximity Correction) và phần

mềm mô phỏng nâng cao để hiệu chỉnh.

- Overlay:

Sai lệch nhỏ khi canh lớp mask này với lớp khác sẽ khiến các lớp không khớp,

gây lỗi chức năng. Tăng số lớp → tăng rủi ro overlay.

- Chi

phí khổng lồ: Mỗi bộ mask (từ 20–80 tấm) có thể tiêu tốn hàng triệu

đô. EUV mask đặc biệt đắt đỏ và khó bảo trì.

6.

Vì sao mask quan trọng?

Photomask là cầu nối giữa thế giới thiết kế logic và sản

xuất vật lý. Không có mask – không thể in được bất kỳ lớp nào của chip.

Không có mask chính xác – cả wafer (hàng trăm chip) có thể trở thành phế phẩm.

Do đó, mask không chỉ là công cụ kỹ thuật, mà còn là một tài

sản chiến lược của các công ty bán dẫn. Mỗi tập tin thiết kế mask được bảo

vệ nghiêm ngặt, mã hóa và kiểm soát chặt chẽ.

Ví dụ, một chip như Apple A17 Pro có thể cần tới 80 mask

khác nhau, với chi phí mask alone đã lên đến hàng chục triệu USD.

7.

Mask trong thực tế

Các hãng chip lớn như Intel, TSMC, Samsung đều có hệ thống

quản lý và sản xuất mask riêng biệt, nằm trong các phòng sạch cấp độ cao nhất.

File thiết kế mask thường được mã hóa bảo mật, chỉ được truy cập bởi các hệ thống

EDA chuyên biệt như Calibre (Mentor), Tachyon (KLA) để kiểm tra lỗi,

mô phỏng chiếu sáng, và hiệu chỉnh OPC.

Mask không chỉ được sản xuất một lần rồi bỏ, mà còn có thể

được tái sử dụng, điều chỉnh hoặc sửa lỗi (mask repair) nếu cần – mặc dù quá

trình này cực kỳ phức tạp và đắt đỏ.

Tối ưu số lượng mask (ví dụ bằng cách dùng multi-patterning)

là một phần quan trọng để giảm chi phí trong các node tiên tiến.

8.

Muốn tìm hiểu thêm?

Bạn có từng nghe đến Inverse Lithography Technology (ILT)

– thuật toán tạo hình mask phức tạp giúp cải thiện độ phân giải?

Hay làm sao để phát hiện và sửa lỗi mask bằng hệ thống

quét quang học, hoặc tại sao cần phòng sạch ISO Class 1 cho EUV mask?

Hãy để lại câu hỏi hoặc cùng tìm hiểu thêm với IC Academy

– nơi kết nối bạn với thế giới vi mạch nhỏ hơn, mạnh hơn và sạch hơn.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận