Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

LEF/DEF – NGÔN NGỮ HÌNH HỌC CỦA CON CHIP

Khi thiết kế vi mạch tiến tới giai đoạn physical design, bạn không

còn làm việc với cổng logic, biểu đồ thời gian hay hàm boolean nữa. Thay vào

đó, mọi thứ bạn xử lý đều là hình học: đường kim loại, tọa độ vị trí, chiều

dài, chiều rộng, khoảng cách giữa các cell, vùng cấm routing,... Trong thế giới

vật lý này, LEF và DEF chính là ngôn ngữ dùng để mô tả mọi thứ: từ hình dáng một

transistor, đến toàn bộ sơ đồ vật lý của con chip.

1. LEF – Thông tin

vật lý của từng cell

LEF (viết tắt của Library Exchange Format) là tệp dữ liệu mô tả

hình dáng vật lý, giới hạn kích thước và đặc điểm layout của từng cell logic

trong thư viện chuẩn (standard cell library).

Nội dung của một file LEF không hề chứa logic hay chức năng hoạt động

của cell. Thay vào đó, nó bao gồm những thông tin sau:

- Kích

thước vật lý của cell: chiều dài, chiều rộng, giúp công cụ biết

cell đó chiếm bao nhiêu diện tích trên die.

- Vị trí

và hướng của các pin: tọa độ pin trong cell, giúp EDA tool có

thể routing các net đúng cách.

- Thông

tin về lớp kim loại được sử dụng: xác định mỗi pin nằm trên metal

layer nào, từ đó công cụ có thể định tuyến một cách chính xác.

- Vùng cấm

routing (OBS – Obstruction): xác định các vùng mà router không

được phép đặt dây dẫn để tránh short hoặc vi phạm DRC.

Ví dụ thực tế:

Giả sử bạn có một thư viện gồm 300 cell cơ bản như INV, NAND, MUX, DFF,... Thay

vì lưu toàn bộ layout của mỗi cell (vốn rất nặng), LEF chỉ giữ lại phần vỏ vật

lý – đủ để layout tool có thể tính toán khi floorplanning và placement.

2. DEF – Sơ đồ lắp

ráp của cả con chip

DEF (Design Exchange Format) là tệp mô tả thiết kế thực tế sau khi bạn

đã hoàn thành các bước place & route. Nếu như LEF là bản thông số kỹ

thuật của từng viên gạch, thì DEF là sơ đồ xây nhà bằng chính những viên gạch

đó.

Một file DEF chứa rất nhiều thông tin chi tiết:

- Danh

sách các cell được sử dụng (COMPONENTS): mỗi cell từ thư viện

được định danh và ghi rõ vị trí tọa độ, hướng đặt (flip, rotate).

- Thông

tin về các net kết nối (NETS): xác định các tín hiệu được nối

giữa các pin của cell nào, thông qua metal layer nào, và theo đường đi

nào.

- Vị trí

chân I/O của toàn chip (PINS): dùng để định vị các chân

input/output, các điểm tiếp xúc của chip với môi trường bên ngoài.

- Kích

thước die area: khai báo vùng thiết kế, tức phần diện

tích khả dụng cho các khối mạch.

- Track,

via, region và các constraint khác: hỗ trợ định tuyến, phân vùng thiết

kế hoặc ràng buộc vật lý cụ thể cho một số khối.

Điểm quan trọng: File DEF được tạo ra sau khi thiết kế logic

đã được tổng hợp (synthesis) và trải qua floorplanning, placement, routing. Nó

là bản snapshot cuối cùng trước khi bạn tape-out chip.

3. Mối liên hệ giữa

LEF và DEF

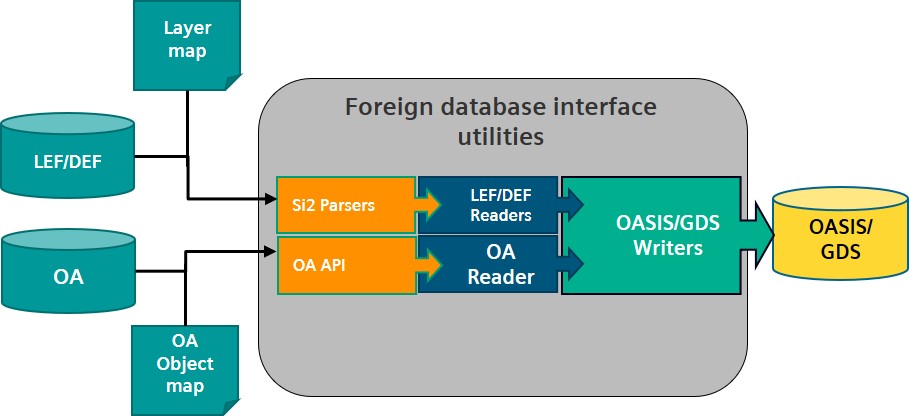

Công cụ EDA như Innovus (Cadence), ICC (Synopsys), hay OpenROAD

(open source) sẽ sử dụng LEF để hiểu hình học của từng cell, và DEF để

lắp ráp toàn bộ thiết kế dựa trên các cell đó.

Cụ thể:

- Trong

bước placement, tool sẽ dùng thông tin từ LEF để đảm bảo không có

cell nào bị chồng lấn.

- Trong

bước routing, tool sẽ dựa vào vị trí pin và vùng OBS trong LEF, kết

hợp thông tin NETS từ DEF để đi dây hợp lý và đúng kỹ thuật.

- Trong

các bước DRC và signoff, tool kiểm tra lại toàn bộ kết nối,

kích thước, điện áp,... dựa trên dữ liệu LEF/DEF.

4. Ứng dụng thực tế:

từ thiết kế logic đến con chip vật lý

Giả sử bạn thiết kế một hệ thống đếm (counter) kết hợp với mạch so

sánh (comparator). Sau khi thiết kế ở mức RTL và tổng hợp ra gate-level

netlist, bạn sẽ tiến hành:

- Dùng

floorplanning để chia bố cục die.

- Place

các cell từ thư viện – quá trình này sẽ tạo thành file DEF mô tả vị trí cụ

thể của từng cell.

- Dùng

routing tool để kết nối các pin – các đường dây này sẽ được lưu lại trong

DEF.

- LEF từ

thư viện chuẩn sẽ hỗ trợ công cụ trong việc sắp xếp và kiểm tra DRC toàn bộ

hệ thống.

Cuối cùng, bạn sẽ gửi LEF + DEF + GDSII (mask layout) để sản

xuất chip thật thông qua chương trình tape-out như MPW (multi-project wafer).

5. Nội dung cụ thể

bên trong file LEF và DEF

LEF bao gồm:

- MACRO:

tên của cell

- SIZE:

kích thước vật lý (micron)

- PIN:

tên pin, lớp kim loại, tọa độ

- OBS:

vùng cấm routing

- LAYER:

xác định loại kim loại sử dụng

DEF bao gồm:

- COMPONENTS:

danh sách các cell đang sử dụng

- NETS:

mô tả các kết nối giữa pin

- PINS: tọa

độ các pin ngoại vi

- DIEAREA:

kích thước vùng thiết kế

- TRACKS,

VIAS, REGIONS: thông tin bổ trợ cho routing

6. Kết luận –

LEF/DEF là cầu nối giữa logic và silicon

LEF và DEF không phải là nơi bạn thể hiện sự sáng tạo logic, nhưng

chúng lại chính là phần quan trọng quyết định thiết kế của bạn có thể được sản

xuất thành công hay không. Mỗi dòng lệnh trong LEF và DEF là một hướng dẫn

tường minh cho công cụ EDA: nên đặt gì, ở đâu, theo chiều nào, nối bằng kim loại

nào, cần tránh vùng nào.

Nếu RTL là phần hồn của con chip – chứa trí tuệ và giải thuật,

thì LEF và DEF chính là phần xác – biểu diễn toàn bộ vật lý, kích thước

và kết nối.

Khi bạn lần đầu tiên xuất ra file DEF và nhìn thấy toàn bộ mạch của

mình trên khuôn chip thông qua công cụ như KLayout hay Magic – đó là khoảnh khắc

kỳ diệu. Bạn không còn thấy mạch điện là thứ trừu tượng nữa, mà là một thực thể

vật lý sẵn sàng bước ra đời thật.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận