Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

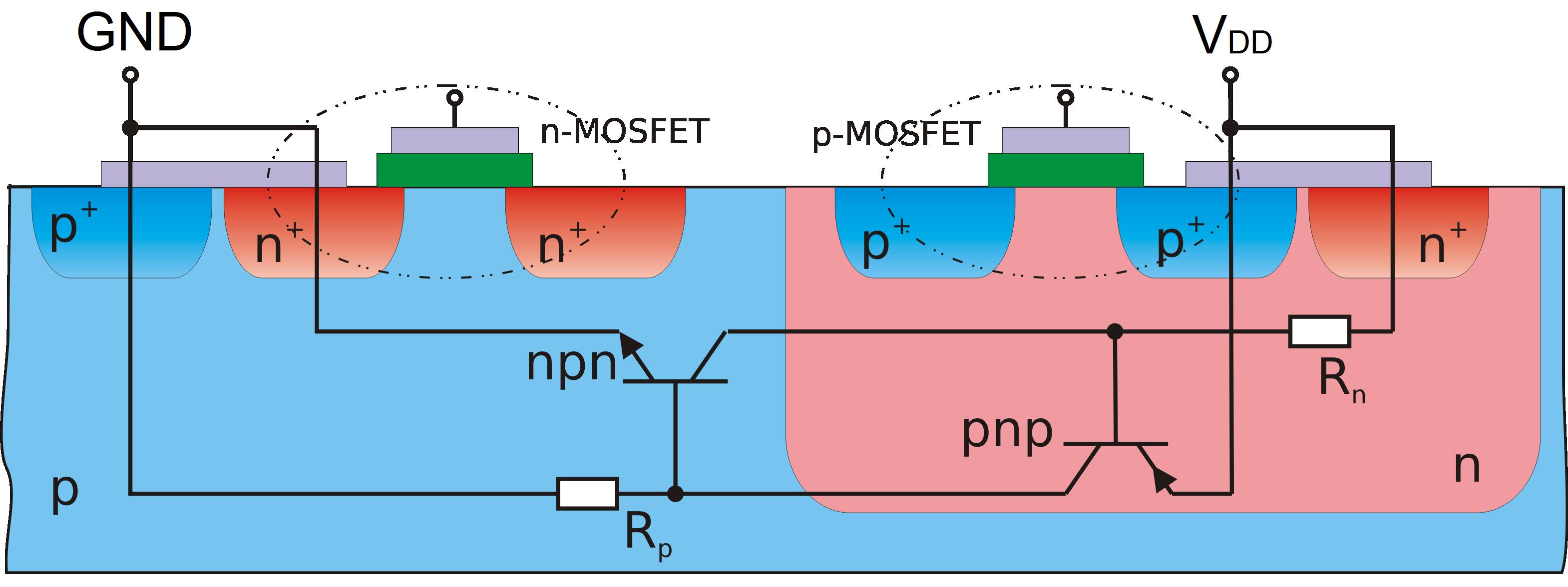

Latch-Up

Định nghĩa

Latch-up là hiện tượng khi có một đường dẫn trở kháng thấp hình thành giữa nguồn cấp và đất. Hiện tượng này xảy ra khi có tác nhân kích thích, chẳng hạn như dòng điện đột ngột hoặc điện áp quá cao, nhưng khi đã xuất hiện, đường dẫn trở kháng thấp này vẫn tồn tại ngay cả khi tác nhân kích thích không còn. Hiện tượng latch-up có thể làm mạch bị lỗi hoặc thậm chí gây hỏng hóc hoàn toàn do dòng điện cao, và cần tắt bật nguồn để loại bỏ tình trạng này.

Trong các mạch CMOS, các transistor NMOS và PMOS thường được bố trí gần nhau, tạo ra các thành phần ký sinh như transistor và diode không mong muốn. Các thành phần ký sinh này tạo nên cấu trúc Thyristor PNPN, với các transistor npn và pnp. Khi điện áp hoặc dòng điện vượt quá mức hoạt động bình thường, các Thyristor PNPN có thể kích hoạt và gây ra latch-up. Điều kiện để latch-up xảy ra là sản phẩm của hệ số khuếch đại của hai transistor ký sinh lớn hơn 1.

Latch-up có thể bắt đầu khi dòng điện đủ lớn chạy qua điện trở, kích hoạt transistor npn. Nếu dòng điện này tạo ra sụt áp đủ lớn, sẽ kích hoạt transistor pnp, và một đường dẫn trở kháng thấp tự duy trì giữa các nguồn điện sẽ hình thành.

Phòng Tránh Latch-Up

Để giảm nguy cơ latch-up, có thể thực hiện các biện pháp sau:

1. Giảm hệ số khuếch đại của các transistor ký sinh:

- Tăng khoảng cách giữa các vùng nguồn/drain và biên của well để hạn chế khả năng hoạt động của các transistor ký sinh.

- Sử dụng lớp n+ chôn trong vùng well sẽ giảm hệ số khuếch đại của transistor pnp.

2. Giảm trở kháng để hạn chế sụt áp:

- Dùng các vòng bảo vệ (guard rings) quanh vùng p-well và n-well với các điểm tiếp xúc thường xuyên giúp các hạt điện được truyền về nguồn hoặc đất.

- Sử dụng các liên kết substrat và well taps giúp tiêu tán các hạt điện.

- Sử dụng lớp epitaxial silicon (EPI) giúp các hạt điện không mong muốn tái hợp nhanh chóng.

3. Cách ly các phần tử ký sinh:

- Sử dụng công nghệ tạo rãnh sâu (deep trenches) để phân tách các nhóm thiết bị giúp giảm thiểu các thành phần ký sinh.

- Công nghệ silicon-on-insulator cùng với rãnh sâu giúp giảm nguy cơ latch-up nhờ khả năng cách ly hoàn toàn.

4. Đảm bảo mạch không vượt quá các giới hạn hoạt động tối đa:

- Dùng mạch bảo vệ chống latch-up (LPT) có khả năng phát hiện latch-up và tắt nguồn chip trong một khoảng thời gian ngắn để giải phóng latch-up.

- Đảm bảo các thiết bị được tắt nguồn trước khi cắm vào mạch để tránh trường hợp "cắm nóng" có thể gây ra latch-up do điện áp quá cao.

- Bảo vệ các thiết bị ESD (bảo vệ chống tĩnh điện) ở các pad I/O bằng các vòng bảo vệ để hạn chế nguy cơ latch-up.

Khi áp dụng các biện pháp trên, nguy cơ latch-up sẽ giảm đáng kể, bảo vệ mạch CMOS an toàn và ổn định hơn.

===

(*) Chú giải các từ viết tắt:

- LVS (Layout Versus Schematic): Kiểm tra Sơ đồ so với Layout

- CMOS (Complementary Metal-Oxide-Semiconductor): Bán dẫn oxit kim loại bổ sung

- NMOS (N-type Metal-Oxide-Semiconductor): Bán dẫn oxit kim loại loại N

- PMOS (P-type Metal-Oxide-Semiconductor): Bán dẫn oxit kim loại loại P

- PNPN Thyristor: Thyristor với cấu trúc bốn lớp bán dẫn (hai lớp P và hai lớp N)

- R_p: Điện trở kết nối đến transistor npn

- R_n: Điện trở kết nối đến transistor pnp

- ESD (Electrostatic Discharge): Phóng tĩnh điện

Nguồn: Lampz

Biên dịch bởi Admin từ iCdemy.com - Đào tạo thiết kế vi mạch chuyên sâu

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận