Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

Kỹ thuật Power Gating (Power Shut-Off - PSO) trong Thiết Kế Vật Lý VLSI

1. Giới thiệu về Power Gating trong VLSI

Power Gating, hay còn gọi là Power Shut-Off (PSO), là một kỹ thuật quản lý nguồn điện tiên tiến trong VLSI (Very Large Scale Integration): Tích Hợp Quy Mô Rất Lớn, nhằm giảm thiểu dòng rò và tiêu thụ điện năng khi hệ thống ở chế độ chờ. Kỹ thuật này chủ yếu được áp dụng cho các phần mạch hoặc mô-đun không cần hoạt động liên tục, chẳng hạn như các khối logic phụ hoặc các phần tính toán không sử dụng thường xuyên, bằng cách ngắt nguồn điện cung cấp cho các mô-đun này.

2. Cơ chế hoạt động của Power Gating

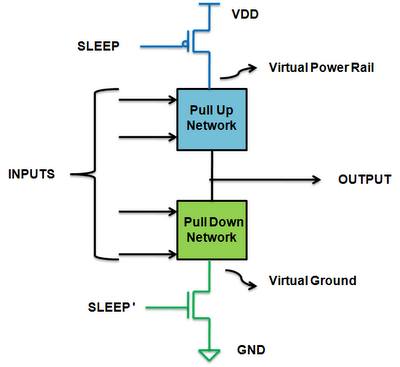

Power Gating được thực hiện thông qua việc sử dụng các switch nguồn - các transistor lớn (thường là transistor NMOS hoặc PMOS) được kết nối giữa nguồn cung cấp (Vdd) hoặc mặt đất (GND) và các mô-đun của mạch. Các switch này sẽ:

- Bật (ON) khi mô-đun cần hoạt động, cho phép dòng điện đi qua và cung cấp năng lượng cho khối mạch.

- Tắt (OFF) khi mô-đun không cần hoạt động, giúp cô lập phần mạch khỏi nguồn cung cấp, qua đó giảm thiểu dòng rò (leakage current).

3. Các Phương Pháp Power Gating

Kỹ thuật Power Gating được triển khai theo nhiều cách khác nhau trong thiết kế VLSI, bao gồm:

- Power Gating Cấp khối (Block-level Power Gating): Cấp nguồn cho các khối hoặc các mô-đun độc lập trong một thiết kế, thường được áp dụng cho các hệ thống lớn để ngắt nguồn của từng khối mạch khi không cần thiết.

- Power Gating theo vùng chức năng (Functional Power Gating): Áp dụng cho các khối chức năng trong mạch, ví dụ như các đơn vị tính toán (ALU) hoặc bộ nhớ cache, khi các phần này không được sử dụng thường xuyên.

- Multi-threshold CMOS (MTCMOS): Sử dụng transistor có ngưỡng điện áp khác nhau (High-Vt và Low-Vt) để giảm thiểu dòng rò, kết hợp với Power Gating giúp tối ưu hóa hiệu quả tiết kiệm điện năng.

4. Các Vấn Đề Kỹ Thuật Liên Quan đến Power Gating

Power Gating đặt ra nhiều thách thức trong thiết kế vật lý, bao gồm:

- Thời gian chuyển trạng thái (Wake-up Time): Khi một phần của mạch được bật lại, sẽ cần một khoảng thời gian để ổn định điện áp và sẵn sàng hoạt động. Điều này có thể gây trễ trong hệ thống, đặc biệt là khi mạch cần đáp ứng nhanh.

- Hiện tượng Inrush Current: Lượng dòng điện lớn sẽ đột ngột tăng khi chuyển từ chế độ tắt sang bật, dẫn đến hiện tượng Inrush Current. Hiện tượng này có thể gây sụt áp đột ngột và ảnh hưởng đến hiệu suất của các phần khác của chip.

- Thiết kế mạch ngủ (Sleep Transistor Design): Các sleep transistor phải được thiết kế với kích thước phù hợp để không gây ảnh hưởng đến hiệu năng và cũng không làm tăng diện tích mạch quá lớn. Kích thước của sleep transistor cần đủ lớn để cung cấp nguồn cần thiết nhưng vẫn phải đảm bảo độ rò rỉ thấp.

5. Quy Trình Thiết Kế Power Gating

Quy trình triển khai Power Gating trong thiết kế vật lý VLSI bao gồm các bước sau:

- Lựa chọn vị trí của các switch nguồn: Các switch nguồn cần được đặt sao cho tối ưu hoá kết nối với các khối mạch và đảm bảo hiệu quả giảm dòng rò mà không ảnh hưởng đến các vùng khác.

- Kết hợp với Multi-threshold CMOS (MTCMOS): Sử dụng transistor với các ngưỡng điện áp khác nhau để cải thiện hiệu quả tiết kiệm năng lượng, qua đó giảm dòng rò nhưng vẫn đảm bảo hiệu suất trong các chế độ hoạt động.

- Sắp xếp bố cục và tối ưu hóa Sleep Transistor: Sleep transistor cần được sắp xếp để tối ưu hóa dòng điện và giảm thiểu Inrush Current. Đảm bảo rằng sleep transistor không bị quá tải khi toàn bộ mô-đun bật lại.

- Kiểm tra và mô phỏng Power Gating: Thực hiện các mô phỏng về hiệu suất nguồn, IR Drop (sụt áp nguồn), tín hiệu timing, và Inrush Current để đảm bảo rằng các yêu cầu về nguồn điện, độ ổn định tín hiệu, và thời gian chuyển trạng thái đều đáp ứng tiêu chuẩn.

6. Ưu và Nhược Điểm của Power Gating

Ưu điểm:

- Tiết kiệm năng lượng hiệu quả: Bằng cách ngắt nguồn cho các mô-đun không cần thiết, Power Gating giúp giảm thiểu dòng rò và tiết kiệm năng lượng đáng kể.

- Giảm nhiệt lượng tỏa ra: Giúp giảm nhiệt độ toàn hệ thống, giúp bảo vệ các linh kiện khỏi nguy cơ quá nhiệt.

- Tăng tuổi thọ mạch tích hợp: Giảm áp lực trên các mạch điện khi không hoạt động, qua đó kéo dài tuổi thọ của mạch.

Nhược điểm:

- Thời gian phục hồi trạng thái chờ: Khi bật lại, mạch sẽ cần một khoảng thời gian để ổn định, gây ra độ trễ.

- Inrush Current lớn: Khi bật lại, có thể xảy ra hiện tượng dòng điện đột ngột tăng lên, ảnh hưởng đến toàn hệ thống.

- Chi phí diện tích mạch lớn: Cần thêm các sleep transistor và switch nguồn, làm tăng diện tích mạch và chi phí sản xuất.

Power Gating là một kỹ thuật quan trọng giúp giảm tiêu thụ năng lượng và dòng rò trong thiết kế VLSI. Mặc dù đòi hỏi các quy trình tối ưu hóa phức tạp và kiểm tra kỹ lưỡng, kỹ thuật này mang lại lợi ích lớn trong việc tiết kiệm điện năng, giảm nhiệt độ, và cải thiện tuổi thọ mạch. Với xu hướng thiết kế vi mạch ngày càng tập trung vào các hệ thống tiết kiệm năng lượng, Power Gating hứa hẹn là một lĩnh vực nghiên cứu và phát triển quan trọng trong các thế hệ chip tương lai.

Nguồn: VLSI SoC

Biên dịch bởi Admin từ iCdemy.com - Đào tạo thiết kế vi mạch chuyên sâu

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận