Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

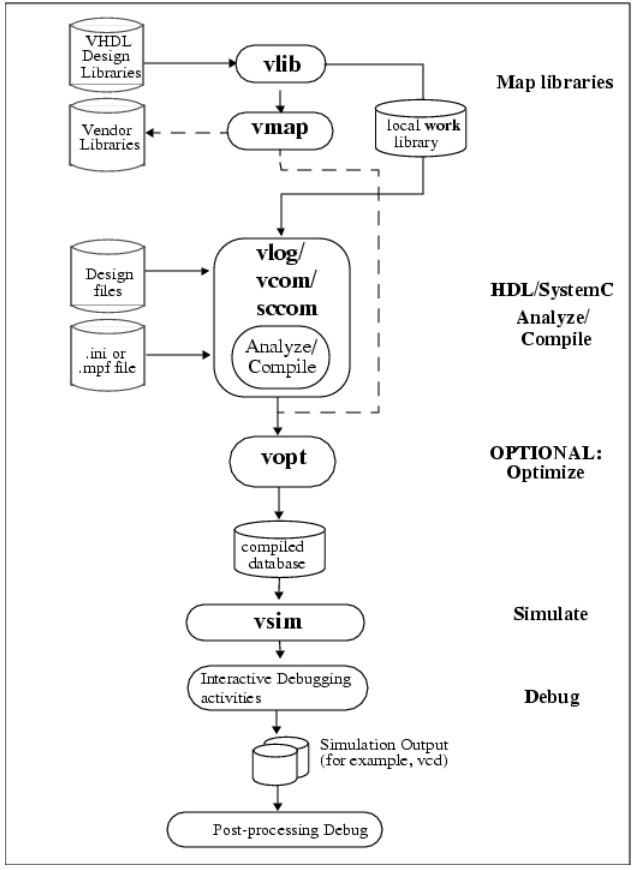

Giới thiệu ngắn về cấu trúc hoạt động và luồng của Questa Sim (Siemens)

Questa SIM là một trong những công cụ mô phỏng phổ biến nhất trong lĩnh

vực thiết kế và xác minh phần cứng. Nó hỗ trợ các ngôn ngữ mô tả phần cứng

(HDL) như VHDL, Verilog, SystemVerilog và cả SystemC,

cho phép kỹ sư kiểm tra tính đúng đắn và hiệu năng của thiết kế trước khi đưa

vào sản xuất.

Questa SIM hoạt động theo một luồng quy trình có cấu trúc, từ bước

thiết lập môi trường cho đến phân tích kết quả mô phỏng. Dưới đây là mô tả chi

tiết từng giai đoạn.

1. Thiết lập thư viện

Quá trình luôn bắt đầu bằng việc tạo và quản lý các thư viện logic

để chứa những đơn vị thiết kế đã biên dịch:

- vlib: Dùng để tạo thư

viện logic mới. Thư viện này có thể là do nhà cung cấp IP cung cấp hoặc do

người dùng tự định nghĩa.

- vmap: Sau khi tạo, thư

viện được ánh xạ với một tên logic bằng lệnh vmap. Bước này liên kết

thư viện vật lý trên đĩa với thư viện logic trong Questa SIM, giúp công cụ

biết nơi lưu trữ các module hoặc entity đã biên dịch.

2. Phân tích và biên dịch mã nguồn

Ở giai đoạn này, các tệp HDL được phân tích cú pháp và biên dịch

thành cơ sở dữ liệu nội bộ của Questa SIM:

- vlog: Dùng cho mã Verilog/SystemVerilog.

- vcom: Dùng cho mã VHDL.

- scccom: Dùng cho mã SystemC.

Người dùng có thể bổ sung các tệp cấu hình như .ini hoặc .mpf để định nghĩa thêm

tùy chọn biên dịch, thư viện liên kết hoặc đường dẫn tìm kiếm file.

3. Tối ưu hóa (tùy chọn)

- vopt: Sau khi biên

dịch, Questa SIM cho phép tối ưu hóa cơ sở dữ liệu thiết kế với lệnh này.

Mục tiêu là giảm độ phức

tạp của mô hình, giúp tăng hiệu suất mô phỏng, đặc biệt quan trọng với các

thiết kế lớn và phức tạp.

4. Mô phỏng và gỡ lỗi

- vsim: Đây là lệnh cốt

lõi để khởi chạy mô phỏng. Người dùng có thể chạy trực tiếp trên mô hình

biên dịch hoặc mô hình đã được tối ưu hóa bằng vopt.

Trong quá trình mô phỏng, Questa SIM cung cấp một môi trường debug

mạnh mẽ:

- Quan sát tín hiệu

qua waveform.

- Đặt breakpoint,

kiểm tra giá trị biến.

- Thực hiện phân tích

theo chu kỳ hoặc theo sự kiện.

Nhờ đó, kỹ sư có thể nhanh chóng tìm ra lỗi thiết kế hoặc điều

chỉnh testbench.

5. Xuất kết quả và xử lý hậu kỳ

Khi mô phỏng hoàn tất, Questa SIM sinh ra các tệp kết quả, ví dụ

như:

- VCD (Value Change

Dump):

Lưu lại biến đổi tín hiệu theo thời gian, phục vụ cho phân tích sau này.

- Các báo cáo thống

kê hoặc dữ liệu coverage (khi bật).

Người dùng có thể tiến hành các bước hậu kỳ như phân tích sâu hơn,

so sánh với kết quả mong đợi hoặc tối ưu hóa lại thiết kế.

Tóm tắt quy trình hoạt động

Toàn bộ luồng hoạt động của Questa SIM có thể tóm gọn như sau:

1. Thiết lập thư viện: Tạo và ánh xạ thư viện

bằng vlib và vmap.

2. Phân tích & biên

dịch: Sử dụng vlog, vcom, hoặc scccom để dịch mã HDL.

3. Tối ưu hóa (tùy chọn): Dùng vopt để tăng tốc mô

phỏng.

4. Mô phỏng & gỡ lỗi: Chạy vsim để mô phỏng, quan

sát waveform, debug tín hiệu.

5. Xử lý hậu kỳ: Phân tích tệp kết quả

(VCD, báo cáo coverage, …) và cải tiến thiết kế.

Kết luận

Với luồng làm việc chặt chẽ và linh hoạt, Questa SIM không

chỉ là một công cụ mô phỏng mà còn là một nền tảng mạnh mẽ để xác minh

và tối ưu hóa thiết kế phần cứng. Việc nắm vững từng bước trong quy trình

này sẽ giúp kỹ sư tiết kiệm thời gian debug, nâng cao chất lượng testbench, và

tăng độ tin cậy của sản phẩm trước khi tape-out.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 92

- 1. Công nghệ vi mạch 50

- 5. Tin tức, Sự kiện và Tuyển dụng 14

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

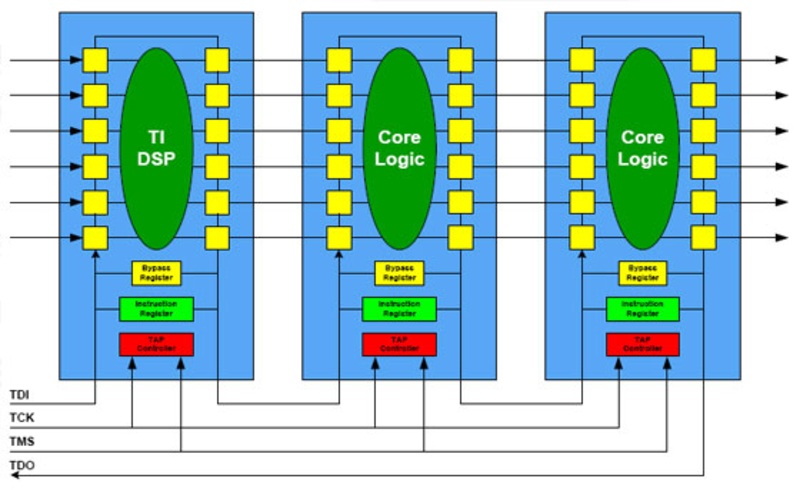

Boundary Scan – Ống nghe kiểm tra mạch không cần tháo tung

Sun, 07 Sep 2025

SDC file - Ràng buộc hoạt động của thiết kế

Sat, 06 Sep 2025

Để lại bình luận