Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

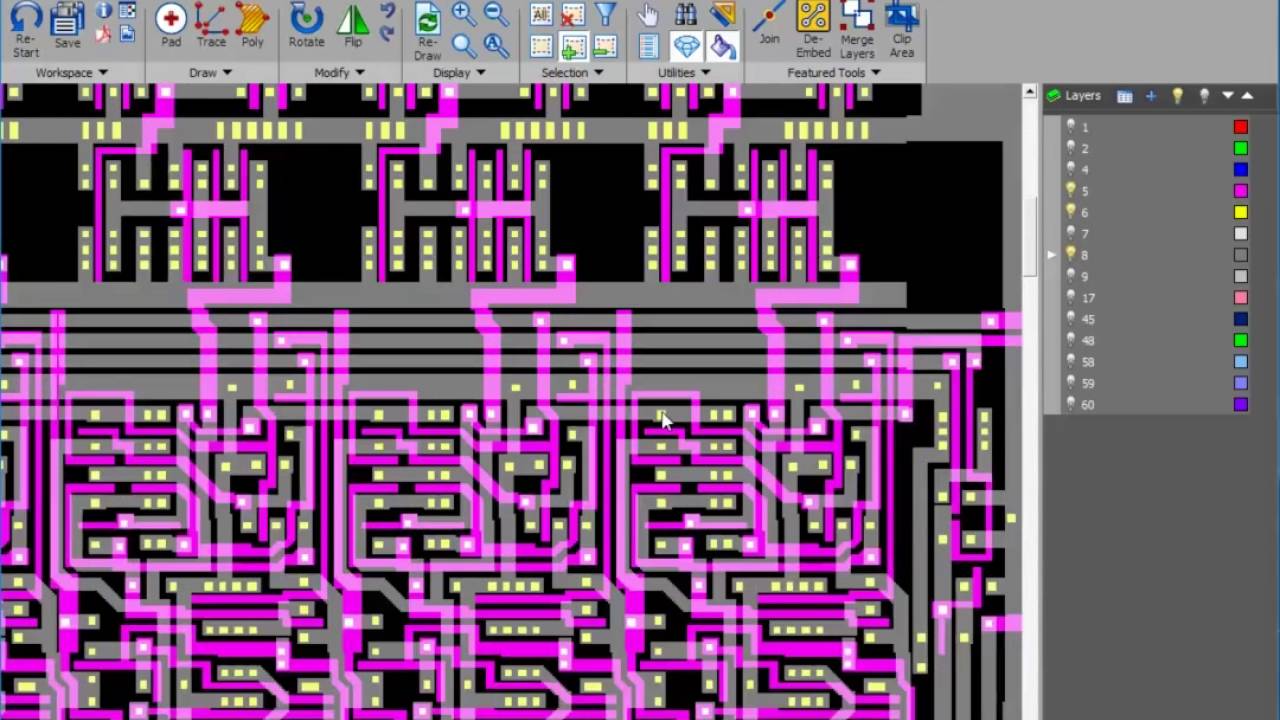

GDSII – TẬP TIN NHỎ, TRÁCH NHIỆM LỚN

Bạn hoàn thành schematic.

Bạn cặm cụi layout từng transistor, từng đường kim loại.

Bạn kiên nhẫn sửa lỗi DRC, vượt qua LVS, tinh chỉnh hàng chục lần.

Và rồi, một ngày, bạn nhấn “Export GDS”.

Kết quả? Một tập tin nhỏ bé, chỉ vài megabyte.

Nhưng bên trong đó là toàn bộ linh hồn của con chip bạn vừa thiết kế.

1. GDSII là gì?

GDSII (Graphic Data System II) là định dạng tập tin tiêu chuẩn dùng để mô tả layout vật lý của mạch tích hợp (IC).

Đây là đầu ra cuối cùng của quá trình thiết kế chip – và cũng là đầu vào cho foundry khi chế tạo silicon.

Nói một cách hình tượng:

-

Nếu RTL là “bản nhạc”

-

Layout là “bản tổng phổ”

-

Thì GDSII chính là “file in ấn bản nhạc” để nhà in tạo ra bản nhạc vật lý thật sự.

Không có GDSII, chip sẽ không thể được sản xuất.

GDSII không chính xác, chip ra lò sẽ lỗi, hoặc tệ hơn — hoàn toàn không hoạt động.

2. Bên trong GDSII có gì?

Một file GDSII không chứa “mạch” theo nghĩa điện học, mà là tập hợp các tọa độ hình học.

Nó bao gồm:

-

Thông tin hình học: kim loại (Metal), poly, diffusion, via/contact.

-

Vị trí & kích thước: mỗi đường, mỗi lớp được mô tả bằng tọa độ chính xác đến nanomet.

-

Hình dạng & thứ tự: đường thẳng, đa giác, cung tròn…

-

Cấu trúc phân cấp (Hierarchy): cell chứa cell con, từ transistor đơn lẻ tới block chức năng phức tạp.

Lưu ý: GDSII không biết đâu là inverter, đâu là op-amp.

Nó chỉ lưu “bạn đã vẽ gì, đặt ở đâu, trên layer nào”.

3. Vai trò của GDSII

GDSII là cầu nối giữa thiết kế và sản xuất.

Nó được sử dụng để:

-

Gửi cho foundry chế tạo IC.

-

Kiểm tra DRC, LVS ở bước cuối.

-

Tạo mask và thực hiện các bước photolithography.

-

Xem và đánh giá layout trong các công cụ như KLayout, Calibre.

4. Ví dụ thực tế

Giả sử một nhóm sinh viên thiết kế chip digital gồm counter và comparator:

-

Viết RTL (Verilog/VHDL).

-

Synthesize sang netlist.

-

Place & Route để ra layout.

-

Kiểm tra DRC pass, LVS pass.

-

Xuất file GDSII và gửi cho chương trình MPW (Multi Project Wafer).

Foundry nhận GDSII từ nhiều nhóm → tổng hợp thành mask → chế tạo wafer.

Vài tháng sau, nhóm nhận lại một con chip nhỏ bằng đầu ngón tay — thành quả từ file GDSII hôm nào.

5. Vì sao GDSII cực kỳ quan trọng?

-

Là bước cuối cùng của toàn bộ quy trình thiết kế IC.

-

Không thể sai sót — một lỗi nhỏ có thể làm cả chip vô dụng.

-

Tập hợp công sức của cả nhóm: từ ý tưởng, thiết kế logic, layout, đến kiểm tra.

-

Dấu ấn hoàn thiện – chứng minh bạn đã hoàn thành một chu trình IC đầy đủ.

6. Lưu ý khi export GDSII cho tape-out

-

Tuân thủ đúng layer theo PDK của foundry.

-

Kiểm tra hierarchy, tránh missing cell.

-

Tránh lỗi reference undefined hoặc empty cell.

-

Chạy lại DRC và LVS trên chính file GDSII.

-

Thêm seal ring, marker, logo nếu chương trình MPW yêu cầu.

7. Kết Luận

GDSII không phải là nơi để sáng tạo, mà là nơi chuyển giao — biến ý tưởng trong EDA tool thành vật chất trên silicon.

Tất cả kỹ năng, cẩn thận, và kiên nhẫn của bạn sẽ được đóng gói trong một tập tin nhỏ bé.

Từ đó, thế giới vật lý bắt đầu.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận