Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

FEOL – NƠI TRANSISTOR RA ĐỜI

Khi bạn "chế tạo chip", bạn đang xây một thành phố vi

mô.

Và Front-End of Line (FEOL) chính là phần "xây móng" –

nơi các transistor được hình thành, định đoạt tốc độ, điện áp, và sức mạnh của

cả vi mạch.

1.

FEOL là gì?

Front-End of Line (FEOL) là giai đoạn đầu tiên trong quá trình chế

tạo vi mạch tích hợp (IC), khi transistor và các thành phần bán dẫn chính như

PMOS, NMOS, diode, tụ điện (capacitor) được hình thành trực tiếp trên silicon

wafer.

Từ một mặt silicon trơn nhẵn, người ta tạo ra hàng tỷ transistor,

đặt nền móng cho các mạch logic, bộ nhớ, mạch tương tự (analog), và nhiều thành

phần khác.

2.

FEOL gồm những

bước nào?

- Oxidation

/ Surface Preparation – tạo lớp SiO₂ cách điện ban

đầu

- Well

Formation – pha tạp để hình thành N-well và P-well

- Isolation

– cách ly giữa các transistor, thường dùng kỹ thuật STI (Shallow Trench

Isolation)

- Ion

Implantation – điều chỉnh đặc tính bán dẫn thông qua doping

- Gate

Stack Formation – hình thành cổng gate (các công nghệ hiện đại thường dùng

HKMG)

- Source/Drain

Implantation – tạo cực nguồn (Source) và thoát (Drain)

- Annealing

– xử lý nhiệt để phục hồi cấu trúc tinh thể sau khi bị ion bắn phá

- Silicidation

– phủ kim loại (thường là nickel hoặc cobalt) để giảm điện trở tiếp xúc

- Sau

FEOL sẽ chuyển sang giai đoạn Middle of Line (MOL) và Backend of Line

(BEOL) để nối dây và hoàn thiện chip

3.

FEOL quyết định

điều gì?

- Tốc độ

switching – transistor càng tốt thì mạch càng nhanh

- Rò rỉ

dòng điện (leakage) – ảnh hưởng bởi độ dày gate oxide, loại doping

- Hiệu suất

năng lượng – ảnh hưởng đến tiêu thụ điện, nhiệt độ

- Chiều

dài kênh (channel length) – càng nhỏ, càng khó chế tạo

- Tỷ lệ lỗi

(yield) – bụi bẩn hay sai sót nhỏ đều dễ làm hỏng cả wafer

4.

Một ví dụ thực

tế:

Giả sử bạn đang chế tạo transistor 5nm – lớp gate oxide chỉ dày

~1nm (chỉ khoảng 5 nguyên tử silicon). Nếu lớp SiO₂ này không đồng đều, sẽ gây rò rỉ điện cực mạnh, dẫn đến hỏng toàn bộ chip.

Hoặc nếu giai đoạn ion implantation chưa tối ưu → điện áp ngưỡng

(threshold voltage) bị lệch → mạch logic tính sai, ảnh hưởng toàn bộ hệ thống.

5.

Công nghệ liên

quan đến FEOL:

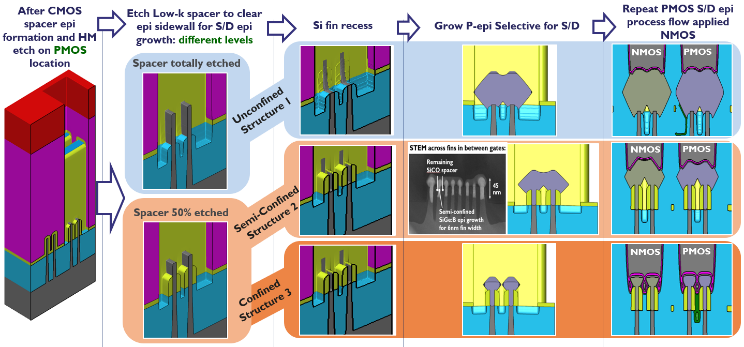

- CMOS –

công nghệ nền tảng sử dụng NMOS và PMOS

- FinFET,

GAAFET – kiến trúc transistor tiên tiến

- HKMG

(High-K Metal Gate) – cải thiện hiệu quả cổng transistor

- SOI

(Silicon-On-Insulator) – giảm rò rỉ, cải thiện cách ly

- EUV

Lithography – in các lớp transistor với độ phân giải siêu nhỏ

6.

Những lưu ý

quan trọng:

- FEOL cực

kỳ nhạy cảm với bụi – một hạt bụi có thể làm hỏng cả die

- Lỗi ở

FEOL → không thể sửa được sau này, vì các bước BEOL không thể

"vá" lỗi từ đầu

- Mỗi thế

hệ node công nghệ mới (7nm, 5nm, 3nm...) đều khiến FEOL trở nên phức tạp

hơn

- Các bước

dopant, gate formation, lithography ở FEOL đều đòi hỏi thiết bị hiện đại,

phòng sạch cấp độ cao

7.

Kết luận:

FEOL là nền móng của vi mạch hiện đại. Nếu transistor là

"trái tim" của con chip, thì FEOL là nơi trái tim ấy được sinh ra – bằng

kỹ thuật chính xác đến từng nguyên tử.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận