Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

Fault Coverage – Thước đo sự tinh mắt của kiểm thử chip

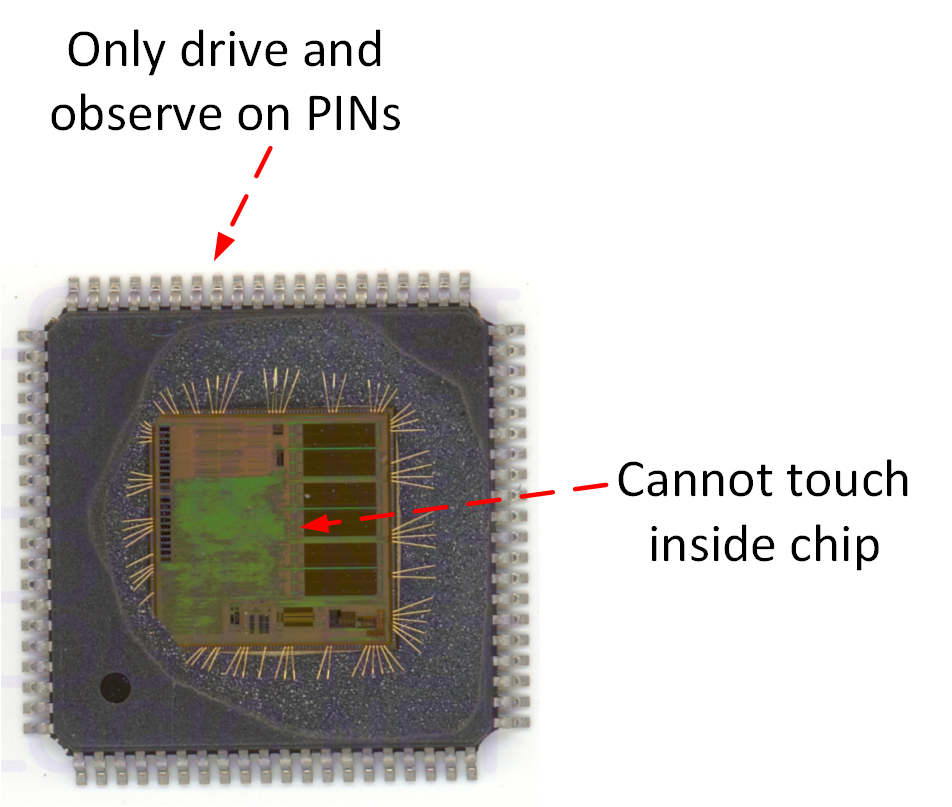

Fault Coverage không chỉ đơn giản là việc phát hiện lỗi trong quá trình kiểm thử vi mạch, mà còn là thước đo đánh giá mức độ bao phủ của các bài kiểm thử đối với những lỗi tiềm ẩn trong chip. Một quy trình test hiệu quả không chỉ cho thấy chip có lỗi hay không, mà quan trọng hơn là đã bao phủ được bao nhiêu phần trăm lỗi có thể xảy ra.

1. Fault Coverage là gì?

Fault Coverage được định nghĩa theo công thức:

Fault Coverage = (Số lỗi được phát hiện / Tổng số lỗi có thể xảy ra) × 100%

Đây là một chỉ số then chốt để đánh giá hiệu quả của quá trình kiểm thử chip.

Nếu Fault Coverage thấp, nghĩa là nhiều lỗi tiềm ẩn vẫn chưa được phát hiện. Điều này rất nguy hiểm bởi các lỗi này có thể gây ra sự cố khi chip đã được sản xuất và đưa ra thị trường.

Nói cách khác, Fault Coverage giống như khám sức khỏe toàn diện: thay vì chỉ xét nghiệm máu, bác sĩ phải kết hợp thêm chụp X-quang, siêu âm, MRI… để đảm bảo không bỏ sót bệnh tiềm ẩn nào.

2. Tại sao Fault Coverage quan trọng?

Trong lĩnh vực vi mạch, Fault Coverage có vai trò đặc biệt quan trọng bởi:

-

Đảm bảo chất lượng sản phẩm: Đối với chip trong máy bay, xe tự lái, hoặc thiết bị y tế, chỉ cần một lỗi nhỏ cũng có thể dẫn đến thảm họa.

-

Giảm rủi ro thương mại: Nếu quá trình kiểm thử không đủ kỹ, sản phẩm lỗi sẽ lọt ra thị trường, dẫn đến thiệt hại hàng triệu đô la do chi phí thu hồi và mất uy tín.

-

Tối ưu chi phí kiểm thử: Việc test toàn bộ 100% lỗi là bất khả thi vì chi phí và thời gian quá lớn. Do đó, mục tiêu là cân bằng giữa phạm vi kiểm thử và chi phí.

Có thể hình dung, kiểm thử chip giống như kiểm tra xe trước một chuyến đi xa: bạn không thể tháo tung toàn bộ động cơ để kiểm tra, nhưng ít nhất phải chắc chắn rằng phanh, đèn, và lốp đã được kiểm tra kỹ lưỡng.

3. Ví dụ thực tế – Thi cử và mức độ bao phủ kiến thức

Giả sử trong một kỳ thi, ngân hàng đề có 100 dạng câu hỏi.

Bạn chỉ ôn luyện được 80 dạng, và trong đề thi có 70 câu trúng phần đã học, còn lại 30 câu chưa gặp.

Như vậy, bạn đã bao phủ được 80% kiến thức.

Trong kiểm thử chip, logic tương tự được áp dụng: Fault Coverage cao nghĩa là bài kiểm thử đã chạm đến càng nhiều loại lỗi tiềm ẩn càng tốt.

4. Các loại Fault Model phổ biến

Để đo lường Fault Coverage, người ta thường dựa trên các Fault Model (mô hình lỗi). Một số mô hình tiêu biểu bao gồm:

-

Stuck-at Fault: Một tín hiệu trong mạch bị “kẹt” vĩnh viễn ở mức logic 0 hoặc 1.

-

Bridging Fault: Hai đường dây trong mạch bị nối nhầm với nhau, gây ra hiện tượng nhiễu.

-

Delay Fault: Tín hiệu truyền qua mạch chậm hơn dự kiến, gây ra lỗi về timing.

-

Transition Fault: Tín hiệu không kịp chuyển đổi trạng thái (từ 0 sang 1 hoặc ngược lại).

Mỗi Fault Model có thể được xem như một “danh sách bệnh” mà kỹ sư cần kiểm tra để chắc chắn rằng con chip không mắc phải.

5. Cơ hội cho kỹ sư Việt Nam

Trong bối cảnh ngành bán dẫn đang phát triển mạnh mẽ, Fault Coverage mở ra nhiều hướng đi cho kỹ sư trẻ Việt Nam:

-

Thiết kế Testbench hiệu quả: Viết testbench bằng Verilog hoặc VHDL với mục tiêu đạt Fault Coverage cao.

-

DFT (Design for Testability): Thiết kế mạch có khả năng tự kiểm thử dễ dàng hơn, với các kỹ thuật như scan chain hoặc BIST (Built-In Self-Test).

-

Phân tích dữ liệu kiểm thử: Sử dụng AI và machine learning để phát hiện những lỗi khó nhận ra bằng phương pháp kiểm thử truyền thống.

-

Cơ hội cho sinh viên: Bắt đầu thực hành với mô phỏng lỗi trong các công cụ như Cadence, Synopsys, Mentor Graphics để làm quen với quy trình Fault Coverage thực tế.

6. Làm thế nào để bắt đầu tìm hiểu Fault Coverage?

Một kỹ sư hoặc sinh viên muốn theo đuổi lĩnh vực này có thể bắt đầu từ:

-

Học lý thuyết: Tìm hiểu các Fault Model cơ bản trong môn học Kiểm thử VLSI.

-

Thực hành ATPG (Automatic Test Pattern Generation): Sử dụng các công cụ để tạo vector kiểm thử tự động.

-

Sử dụng phần mềm chuyên dụng: Các công cụ phổ biến như Tetramax (Synopsys) giúp đo và phân tích Fault Coverage.

-

Đọc tài liệu chuyên sâu: Tham khảo các tài liệu IEEE và sách chuyên ngành về testability và fault simulation.

Kết luận

Fault Coverage không chỉ đơn thuần là một con số phần trăm, mà chính là thước đo độ “tinh mắt” của quy trình kiểm thử chip.

Một hệ thống kiểm thử hiệu quả không chỉ giúp phát hiện lỗi, mà còn chứng minh rằng mọi ngóc ngách tiềm ẩn đã được soi xét kỹ càng.

Đối với kỹ sư trẻ Việt Nam, tìm hiểu về Fault Coverage chính là bước đi quan trọng để tiến vào thế giới DFT (Design for Testability) và kiểm thử vi mạch – nơi mà từng phần trăm nhỏ của chỉ số này có thể quyết định sự thành công hay thất bại của cả một con chip.

Thẻ:

iCdemy Fault Coverage Chip Testing Test Quality Design for Testability Fault Models Verification & Validation Automatic Test Equipment thiết kế vi mạch0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận