Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

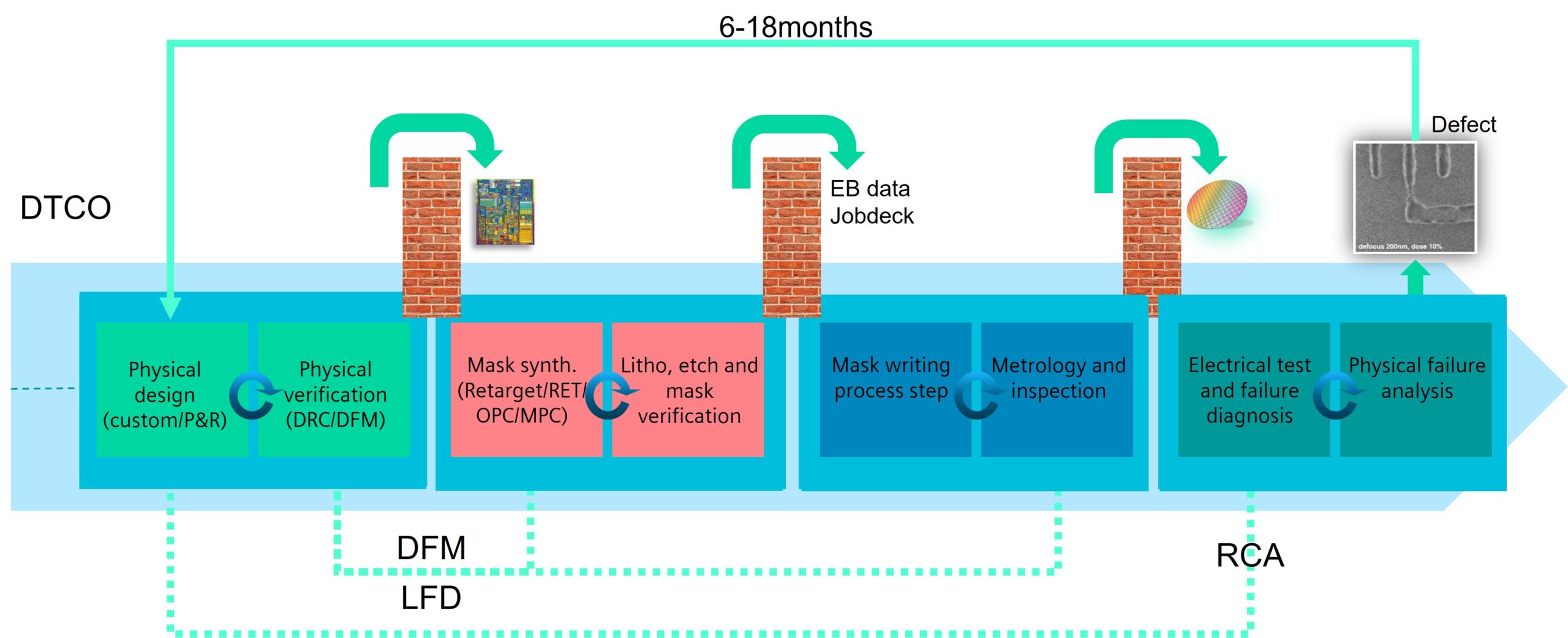

DTCO – KHI CHUYỆN THIẾT KẾ KHÔNG CÒN LÀ VIỆC RIÊNG CỦA DESIGNER

Bạn miệt mài tối ưu RTL, thiết kế layout thật nhỏ gọn,

chọn standard cell phù hợp để đạt hiệu năng tốt nhất. Trên công cụ mô phỏng,

các chỉ số PPA (Performance – Power – Area) đều rất ấn tượng. Nhưng khi tape-out,

silicon thật ra đời – thì chip lại chạy chậm hơn kỳ vọng, tiêu thụ nhiều

điện hơn, và thậm chí nóng bất thường.

Lúc đó, bạn mới nhận ra: một con chip không chỉ thành công nhờ

thiết kế tốt. Nó còn phụ thuộc vào công nghệ chế tạo phía sau. Và nếu

thiết kế chỉ lo phần mình, còn công nghệ đi một hướng khác, chip tạo ra sẽ không

bao giờ tối ưu thực sự.

Đó là lý do Design Technology Co-Optimization (DTCO) ra đời

– để thiết kế và công nghệ “bắt tay nhau” ngay từ đầu.

1.

DTCO là gì?

Design Technology Co-Optimization (DTCO) là quá

trình phối hợp chặt chẽ giữa team thiết kế (design) và team công nghệ

chế tạo (technology) để đồng thời tối ưu hiệu suất, năng lượng và diện

tích của chip.

Thay vì cách làm truyền thống:

“Công nghệ làm xong rồi, design cứ thế mà dùng.”

DTCO đề xuất một tư duy mới:

“Cùng phát triển. Cùng thử nghiệm. Cùng tối ưu. Và cùng chiến thắng.”

2.

Vì sao cần

DTCO?

Khi tiến trình công nghệ ngày càng thu nhỏ (từ 7nm → 5nm →

3nm…), các vấn đề vật lý trở nên nghiêm trọng hơn và không thể giải quyết

bằng cách tối ưu riêng lẻ từng phần. Một số thách thức tiêu biểu gồm:

- Transistor nhỏ

hơn → rò rỉ lớn hơn

- Dây kim

loại mảnh hơn → trở kháng tăng

- Fanout

nhiều → delay tăng mạnh

- Các chuẩn

cell truyền thống không còn hiệu quả vì không phù hợp với pitch dây và

đặc tính mới của transistor.

Muốn vượt qua các rào cản này, cần có sự đồng bộ giữa thiết kế

và công nghệ chế tạo – và DTCO chính là chiếc cầu nối đó.

3.

DTCO diễn ra

như thế nào?

Trong thực tế, DTCO không chỉ là một khái niệm, mà là một

chuỗi hành động cụ thể và phối hợp liên tục:

- Thiết kế

Standard Cell mới dựa trên công nghệ FinFET hoặc GAA.

- Tối ưu

lại layout của SRAM dựa trên khả năng ổn định điện áp và nhiễu

thực tế.

- Phân

tích tác động của các yếu tố như chiều cao kim loại, khoảng cách giữa

các lớp dây, vật liệu dây… đến độ trễ tín hiệu và nhiệt độ.

- Chỉnh sửa

kiến trúc logic để tương thích với pitch kim loại mới và các

hạn chế vật lý từ tiến trình công nghệ.

Các công cụ EDA hiện đại như Synopsys Fusion Compiler,

Cadence Innovus, hoặc Mentor Calibre hiện nay đều đã hỗ trợ môi

trường thiết kế tích hợp theo DTCO.

4.

Ví dụ thực tế:

tối ưu chuẩn cell cho tiến trình 5nm

Giả sử bạn đang thiết kế một core CPU ở tiến trình 5nm.

Để tiết kiệm diện tích, bạn chọn standard cell 9-track. Tuy nhiên, sau

khi tổng hợp và layout, delay tăng cao, khiến bạn phải chèn thêm buffer

– làm tăng power tiêu thụ.

Sau khi làm việc với team process, cả hai bên quyết định phát triển

một cell 10.5-track với chiều cao cell phù hợp hơn với pitch dây tầng

M1–M3. Kết quả thu được:

- Delay cải

thiện 18%

- Số

buffer giảm đáng kể

- Tổng

năng lượng tiêu thụ giảm 12%

Thành quả này không thể đạt được nếu design và technology làm

việc tách biệt.

5.

Sau khi áp dụng

DTCO, bạn có thể làm gì?

- Tối ưu

kiến trúc logic theo transistor mới như GAA

hoặc nanosheet.

- Thiết kế

SRAM có khả năng hoạt động ổn định hơn dưới biến thiên điện áp

và nhiệt độ.

- Rút ngắn

thời gian tape-out nhờ mô hình điện chính xác hơn.

- Phát hiện

sớm các "nút thắt cổ chai" về delay, power, hoặc nhiệt

độ từ giai đoạn early design.

6.

Kết luận: DTCO

không còn là lựa chọn – mà là điều bắt buộc

Trong một thời đại mà mỗi nanomet đều phải đổi bằng công

sức – thời gian – và tiền bạc, việc thiết kế một con chip tối ưu đòi hỏi design

và technology phải cùng hướng.

Bạn không thể thiết kế một chip tốt nếu chỉ dựa vào công cụ mô phỏng.

Bạn cần hiểu và phối hợp với cả công nghệ tạo ra nó.

Thẻ:

DTCO DesignTechCoOptimization ChipCoDesign ICDesignFlow HocICcungICdemy thiết kế vi mạch iCdemy0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận