Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

Design for Testability – Nghệ thuật biến kiểm thử thành một phần của thiết kế

Khi thiết kế chip không chỉ để chạy, mà còn để kiểm thử

Trong ngành bán dẫn, việc thiết kế một con chip có thể hoạt động đúng chức năng vốn đã là một thử thách khổng lồ. Nhưng chỉ dừng lại ở mức “chạy được” là chưa đủ. Để một con chip thương mại thực sự đi vào sản xuất hàng loạt, nó cần được kiểm thử (test) một cách nhanh chóng, hiệu quả và toàn diện.

Đó chính là lý do ra đời của DFT (Design for Testability) – “thiết kế để dễ test”.

1. DFT là gì?

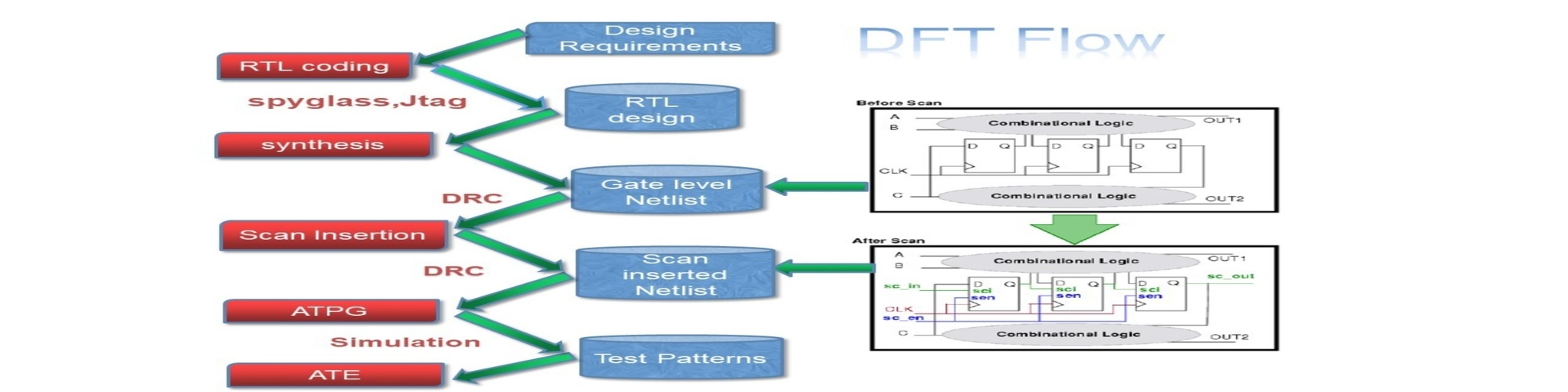

Design for Testability (DFT) là tập hợp các kỹ thuật được thêm vào trong quá trình thiết kế chip, nhằm hỗ trợ kiểm thử hiệu quả hơn. Thay vì đợi đến khi chip đã sản xuất xong mới “vật lộn” với việc test, DFT cho phép chuẩn bị ngay từ khâu RTL/logic design.

Một cách hình tượng, nếu chip là một ngôi nhà, thì DFT chính là việc xây sẵn cửa sổ, lối thoát hiểm và hệ thống đường điện phụ để dễ dàng quan sát, kiểm tra và bảo trì. Không có DFT, kỹ sư kiểm thử sẽ như người phải tìm lỗi trong một căn nhà kín mít, không cửa ra vào.

2. Tại sao DFT quan trọng?

-

Chip ngày càng phức tạp: Một SoC hiện đại có thể chứa hàng tỷ transistor. Việc kiểm thử thủ công là bất khả thi, cần những kỹ thuật đặc thù.

-

Tiết kiệm chi phí: Kiểm thử có thể chiếm tới 30% giá thành một con chip. Nếu thiết kế ngay từ đầu đã có DFT, chi phí kiểm thử sẽ giảm mạnh nhờ thời gian test ngắn hơn và khả năng tự động hóa cao hơn.

-

Đảm bảo chất lượng: DFT cho phép đạt Fault Coverage cao, nghĩa là phát hiện được nhiều loại lỗi hơn → giảm nguy cơ chip lỗi lọt ra thị trường.

-

Khả năng mở rộng: Với DFT, cùng một kiến trúc test có thể áp dụng cho nhiều thế hệ chip, tiết kiệm công sức về lâu dài.

Một ví dụ quen thuộc: giống như khi thi công cầu đường, nếu không thiết kế sẵn các lối kiểm tra và bảo dưỡng, thì việc duy tu sau này sẽ cực kỳ tốn kém và phức tạp. Với chip, chi phí sửa chữa lỗi sau khi tape-out có thể lên tới hàng triệu đô.

3. Ví dụ thực tế – Ôn thi có “phao”

Hãy tưởng tượng bạn đi thi:

-

Nếu không chuẩn bị trước, bạn phải giải từng bài từ đầu, vừa lâu vừa dễ sai sót.

-

Nếu đã có bảng tóm tắt (phao ôn tập), bạn chỉ cần đối chiếu nhanh để xử lý hiệu quả.

Trong thiết kế chip, DFT chính là “phao” giúp cho việc kiểm thử không còn kéo dài hàng tháng trời mà có thể thực hiện nhanh chóng, đảm bảo độ bao phủ lỗi (coverage) cao.

4. Các kỹ thuật DFT phổ biến

-

Scan Chain: Thay vì test từng flip-flop riêng lẻ, chúng được nối thành một chuỗi (chain) giúp dễ dàng điều khiển và quan sát trạng thái bên trong chip.

-

BIST (Built-In Self-Test): Chip có khả năng tự kiểm thử chính nó, đặc biệt quan trọng đối với bộ nhớ (Memory BIST). Nó giống như một “bác sĩ tự khám sức khỏe”.

-

Boundary Scan (JTAG – IEEE 1149.1): Cho phép kiểm tra kết nối giữa chip và PCB, cực kỳ hữu ích trong sản xuất board mạch.

-

ATPG (Automatic Test Pattern Generation): Công cụ tự động sinh vector test để đạt Fault Coverage cao nhất.

Mỗi kỹ thuật DFT giống như một công cụ khám bệnh chuyên sâu, hỗ trợ kỹ sư kiểm tra con chip ở nhiều “góc độ sức khỏe” khác nhau.

5. Cơ hội cho kỹ sư Việt Nam

Trong bối cảnh ngành bán dẫn tại Việt Nam đang phát triển, DFT là một trong những mảng mà kỹ sư trẻ có thể tham gia ngay từ giai đoạn đầu.

-

Thiết kế & viết testbench DFT: Sử dụng Verilog/VHDL để mô phỏng fault coverage.

-

Học các công cụ EDA: Thành thạo các tool của Synopsys (DFT Compiler, Tetramax), Cadence, Mentor Graphics.

-

Ứng dụng AI trong Test: Dùng machine learning để tối ưu test pattern hoặc dự đoán lỗi.

-

Sinh viên & người mới bắt đầu: Có thể thử với các project nhỏ như scan chain cho mạch đơn giản, hoặc mô phỏng Memory BIST cho RAM.

6. Bắt đầu học DFT như thế nào?

-

Nắm chắc nền tảng: Digital Design, Flip-Flop, FSM, Logic Gate.

-

Học các mô hình lỗi (Fault Model): Stuck-at Fault, Transition Fault, Bridging Fault…

-

Thực hành với công cụ công nghiệp: Tetramax, DFT Compiler, hoặc open-source test tools.

-

Đọc tài liệu chuyên sâu:

-

Digital Systems Testing and Testable Design – Abramovici.

-

Các tiêu chuẩn IEEE liên quan đến Boundary Scan và BIST.

-

-

Tham gia dự án thực tế: Một module nhỏ cũng có thể là nơi để chèn scan chain, từ đó hiểu cách ATPG hoạt động.

7. Kết luận

DFT không làm chip chạy nhanh hơn, nhưng làm chip đáng tin cậy hơn.

Trong kỷ nguyên hàng tỷ transistor, DFT chính là chìa khóa để ngành bán dẫn duy trì chất lượng, giảm chi phí và đảm bảo tiến độ sản xuất.

Với kỹ sư trẻ Việt Nam, DFT là một trong những hướng đi đầy tiềm năng trong IC Design & Verification, nơi mà khả năng “soi lỗi” chính là lợi thế cạnh tranh lớn nhất.

Thẻ:

iCdemy Design for Testability DFT Chip Testing Fault Coverage Verification & Validation Automatic Test Equipment Scan Design thiết kế vi mạch0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận