Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

Coverage-driven Verification (CDV) – Vì Sao Nó Quan Trọng Trong Design Verification?

Trong lĩnh vực Design Verification (DV), nhiệm vụ quan trọng không chỉ dừng lại ở việc xây dựng testbench và chạy simulation, mà còn phải đảm bảo rằng thiết kế đã được kiểm thử toàn diện và có độ bao phủ đầy đủ. Đây chính là lý do mà Coverage-driven Verification (CDV) trở thành một phương pháp tiếp cận then chốt trong quy trình xác minh phần cứng hiện đại.

1. Khái niệm Coverage trong Verification

Coverage là thước đo thể hiện mức độ mà các phần trong thiết kế đã được kiểm tra thông qua simulation. Nói cách khác, coverage trả lời những câu hỏi sau:

-

Liệu tất cả các đường logic trong thiết kế đã được kích hoạt chưa?

-

Có tình huống hoạt động nào chưa từng được kiểm thử không?

-

Có ngóc ngách nào trong thiết kế mà testbench không bao giờ chạm tới không?

Việc theo dõi coverage không chỉ giúp xác định những gì đã được test, mà quan trọng hơn là phát hiện những khoảng trống trong quá trình xác minh.

2. Các loại Coverage trong CDV

Trong môi trường Coverage-driven Verification, coverage được phân thành nhiều loại để đảm bảo kiểm thử từ nhiều góc độ khác nhau:

-

Code Coverage: Đo lường mức độ mà mã RTL đã được kích hoạt trong quá trình simulation. Bao gồm:

-

Line Coverage: Tất cả các dòng RTL đã được chạy qua hay chưa.

-

Branch Coverage: Các nhánh của điều kiện if/else đã được thực hiện đầy đủ hay chưa.

-

Condition Coverage: Mỗi điều kiện logic trong thiết kế đã được kiểm tra cả true và false hay chưa.

-

-

Functional Coverage: Do Verification Engineer định nghĩa, nhằm đảm bảo rằng tất cả các scenario quan trọng trong thiết kế đều được kiểm thử. Đây là dạng coverage phản ánh yêu cầu thiết kế thay vì chỉ phụ thuộc vào code RTL.

-

Toggle Coverage: Xác minh rằng tất cả các tín hiệu trong thiết kế đều đã thay đổi trạng thái từ 0 → 1 và 1 → 0 ít nhất một lần, giúp phát hiện các tín hiệu "chết" (never toggled).

-

FSM Coverage: Đảm bảo rằng tất cả các trạng thái (state) và chuyển tiếp trạng thái (transition) trong một Finite State Machine đã được kích hoạt đầy đủ.

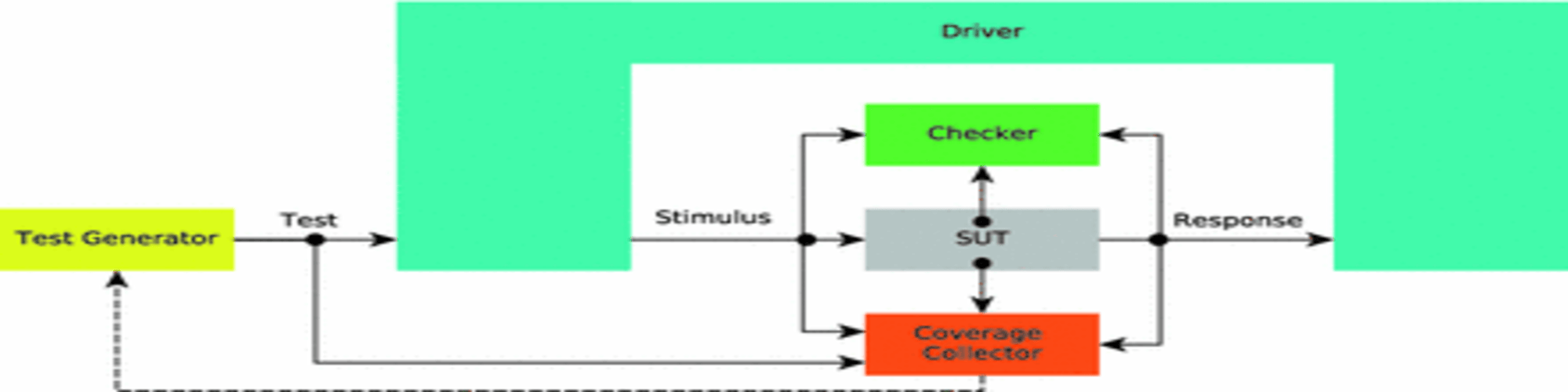

3. Cơ chế hoạt động của Coverage-driven Verification

Quy trình CDV thường bao gồm các bước sau:

-

Randomization: Sử dụng các cơ chế sinh input stimulus ngẫu nhiên có ràng buộc (constrained-random stimulus) để khám phá nhiều tình huống khác nhau thay vì chỉ test theo kịch bản thủ công.

-

Functional Coverage Points: Xác định các coverpoint và cross coverage để đo lường những hành vi, điều kiện hoặc tổ hợp mà testbench đã kiểm tra.

-

Coverage Analysis: Sau khi simulation, báo cáo coverage sẽ chỉ ra những phần nào trong thiết kế đã được kiểm tra và những phần nào còn chưa được chạm tới.

-

Refinement: Viết thêm test case, chỉnh sửa constraint, hoặc bổ sung directed test để lấp đầy các lỗ hổng coverage.

Quá trình này mang tính lặp lại (iterative) cho đến khi đạt mức coverage mong muốn (coverage closure).

4. Tầm quan trọng của CDV

CDV mang lại nhiều lợi ích quan trọng trong thực tiễn Design Verification:

-

Giảm rủi ro bug lọt ra silicon: Việc coverage không đầy đủ có thể dẫn đến việc các lỗi nghiêm trọng không được phát hiện trước khi tape-out, gây tốn kém chi phí và thời gian.

-

Tối ưu hóa thời gian kiểm thử: Thay vì viết test tùy ý và có khả năng trùng lặp kịch bản, CDV tập trung vào những phần chưa được kiểm tra, giúp tiết kiệm đáng kể công sức và thời gian.

-

Đảm bảo chất lượng sản phẩm: Coverage là bằng chứng khách quan chứng minh rằng quá trình DV đã được tiến hành một cách có hệ thống và toàn diện.

-

Chuẩn hóa quy trình DV: CDV giúp các team verification xây dựng quy trình chuẩn mực, dễ dàng mở rộng và áp dụng lại cho các dự án khác.

5. So sánh CDV với cách tiếp cận truyền thống

-

Trong cách tiếp cận truyền thống, verification thường dựa vào directed test – viết test case cụ thể cho từng scenario. Nhược điểm là khó bao quát toàn bộ thiết kế và dễ bỏ sót case hiếm.

-

Với Coverage-driven Verification, thay vì “test càng nhiều càng tốt”, chúng ta chuyển sang “test đủ và đúng trọng tâm”. CDV kết hợp random test và functional coverage để đạt coverage closure một cách hiệu quả hơn.

6. Kết luận

Coverage-driven Verification (CDV) không chỉ là một kỹ thuật, mà là một tư duy xác minh hiện đại. Thay vì chạy hàng nghìn simulation vô nghĩa, CDV cho phép các kỹ sư tập trung vào lỗ hổng chưa được kiểm tra, đảm bảo rằng thiết kế được kiểm thử một cách toàn diện, khoa học và có bằng chứng cụ thể.

Trong bối cảnh các thiết kế chip ngày càng phức tạp, hàng tỷ transistor và nhiều kịch bản hoạt động khó lường, CDV trở thành công cụ bắt buộc để giúp đội ngũ verification đạt được tape-out an toàn, tiết kiệm chi phí và nâng cao chất lượng sản phẩm.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận