Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

CMP – CÀO PHẲNG CẢ THẾ GIỚI VI MẠCH

Bạn không thể xây nhà trên nền đất lồi lõm. Với chip cũng vậy

– sau mỗi lớp transistor, kim loại, cách điện… bề mặt wafer phải phẳng tuyệt

đối trước khi xây tiếp tầng sau. Bất kỳ sự gồ ghề, không đồng đều nào cũng

sẽ khiến lớp sau bị sai lệch, gây lỗi nghiêm trọng trong toàn bộ vi mạch.

Đó là lý do CMP (Chemical Mechanical Planarization)

ra đời – một kỹ thuật cốt lõi của ngành chế tạo bán dẫn hiện đại, kết hợp giữa

lực cơ học và phản ứng hóa học để làm phẳng bề mặt wafer với độ chính xác… đến

cấp độ nguyên tử.

1.

CMP là gì?

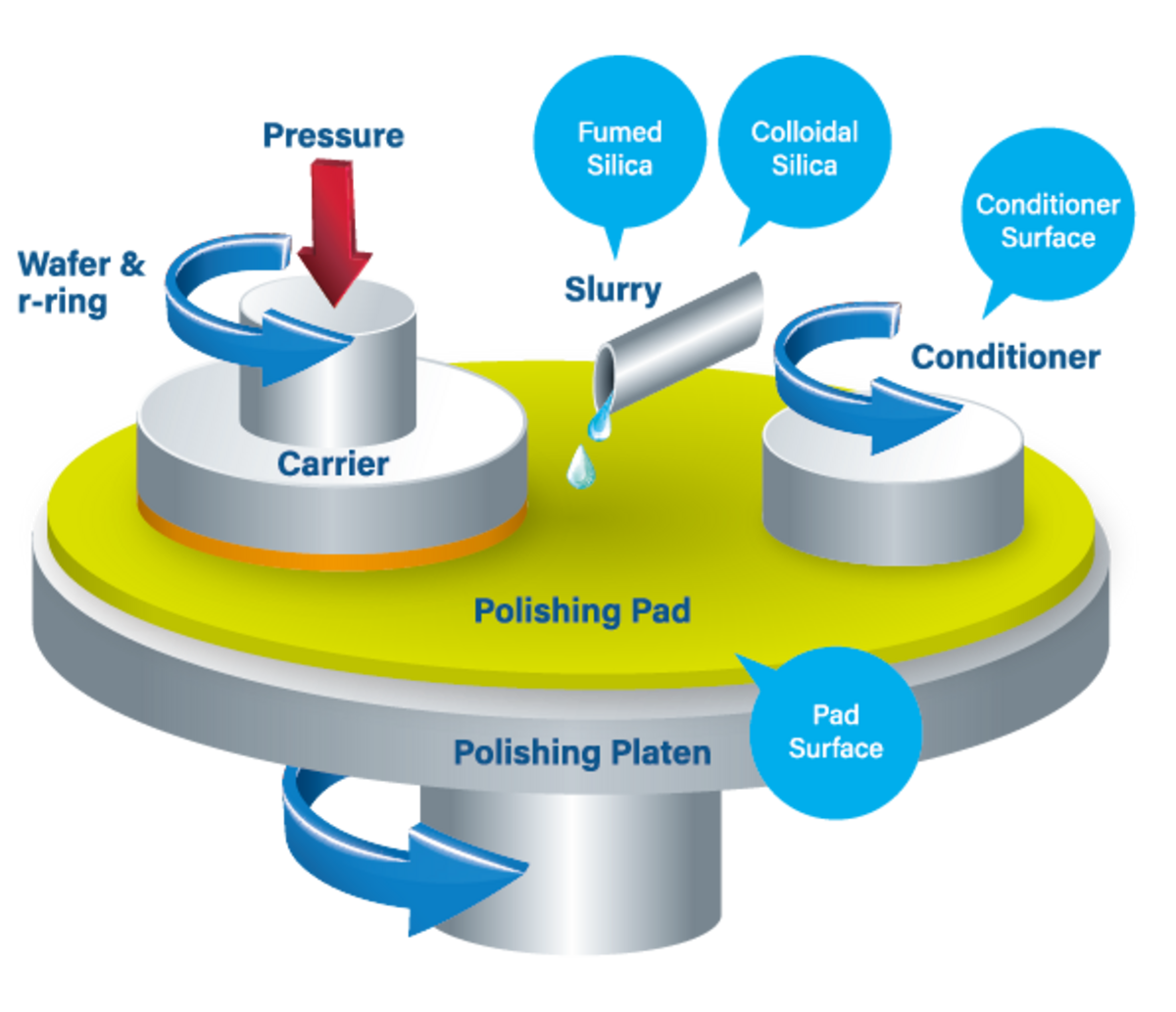

CMP là quá trình làm phẳng bề mặt wafer bằng

cách kết hợp giữa đệm mài quay tròn (pad) và dung dịch mài mòn

(slurry). Dưới áp lực nhẹ, wafer được ép sát vào pad đang quay, trong khi

slurry được phân phối đều lên bề mặt, thực hiện đồng thời:

- Mài

cơ học: các hạt mài nhỏ mài mòn phần vật liệu dư thừa.

- Phản

ứng hóa học: các thành phần hóa học trong slurry giúp “ăn mòn” có chọn

lọc vật liệu mong muốn.

- Làm

sạch tức thì: giúp loại bỏ vật liệu đã hòa tan.

Tất cả diễn ra đồng thời trong điều kiện được kiểm soát cực

kỳ chặt chẽ: tốc độ quay, áp lực, nhiệt độ, pH slurry, độ phân bố hạt, v.v.

2.

CMP dùng ở đâu?

CMP xuất hiện ở hầu hết các giai đoạn trong quy trình chế

tạo chip, đặc biệt là:

- FEOL

(Front-End-Of-Line): làm phẳng bề mặt sau khi tạo rãnh STI (Shallow

Trench Isolation), lớp cổng (gate), hoặc lớp tiếp xúc silicide.

- BEOL

(Back-End-Of-Line): làm phẳng mỗi lớp kim loại và lớp via, giúp dây dẫn

có hình dạng chính xác và đảm bảo ăn khớp với lớp sau.

- Dual

Damascene: sau khi mạ đồng, CMP được dùng để loại bỏ phần đồng dư, chỉ

giữ lại đồng trong các trench và via.

- Wafer

Bonding / TSV stacking: đảm bảo các wafer phẳng tuyệt đối trước khi

dán chồng lên nhau – nền tảng của công nghệ 3D IC hiện đại.

3.

Tại sao CMP quan trọng?

- Phẳng

để in chính xác: các bước quang khắc (lithography) chỉ hiệu quả nếu bề

mặt chip bằng phẳng tuyệt đối. Gồ ghề = lớp sau lệch = lỗi sản xuất.

- Phẳng

để stacking: TSV, chiplet, wafer bonding… đòi hỏi wafer không chỉ phẳng

mà còn cực kỳ đồng đều về độ cao (planarity).

- Phẳng

để tăng yield: sự không đồng đều dẫn đến hiện tượng mạch đứt, ngắn mạch,

gây hỏng chip dù transistor vẫn hoạt động tốt.

- Phẳng

để kiểm tra được: ảnh SEM đẹp, phân tích E-beam chính xác hơn, giảm

công sức debug sau này.

4.

CMP bao gồm những thành phần gì?

- Pad

mài: thường làm từ polyurethane hoặc vật liệu nonwoven, quay liên tục

với tốc độ hàng trăm RPM.

- Slurry:

dung dịch mài mòn chứa hạt nano (SiO₂, CeO₂…) + hóa chất hòa tan (acid, oxi hóa…).

- Endpoint

Detection: hệ thống cảm biến theo dõi độ phẳng và nhận biết khi cần dừng

quá trình.

- Post-CMP

Cleaning: bước rửa sạch wafer để loại bỏ các hạt mài và hóa chất còn

sót lại.

- Defect

Control: kiểm soát lỗi như trầy xước (scratch), lõm (dishing), xói mòn

(erosion).

5.

Ví dụ minh họa

Giả sử bạn vừa mạ lớp đồng cho tầng kim loại M3. Lúc này, đồng

phủ kín toàn bộ bề mặt wafer, không theo hình dạng mạch mong muốn. CMP được sử

dụng để mài đi phần đồng dư, chỉ giữ lại đồng trong các trench và via

đã khắc từ trước. Kết quả: mạng lưới kim loại M3 đúng như thiết kế, lớp tiếp

theo có nền phẳng để tiếp tục xây dựng.

Hoặc: trong công nghệ 3D TSV stacking, nếu wafer sau

CMP không phẳng hoàn toàn → lớp chip đặt lên bị lệch → TSV không khớp → toàn

bộ hệ thống 3D IC không hoạt động.

6.

Những thách thức và lưu ý với CMP

- Quá

mài → Erosion: khiến các trench bị ăn mòn quá mức.

- Không

đều → Dishing: vùng đồng lõm xuống giữa trench → điện trở tăng, hiệu

suất giảm.

- Slurry

sai = phá wafer: mỗi vật liệu (đồng, oxit, tantalum…) cần loại slurry

khác nhau – chọn sai là hỏng cả lô.

- Chi

phí lớn: pad và slurry tiêu hao nhanh, hệ thống CMP đắt đỏ.

- Yêu

cầu kiểm soát nghiêm ngặt: lực mài, phân phối slurry, tốc độ pad, độ đồng

đều trên toàn bề mặt wafer…

7.

Kết luận

CMP là “nghệ thuật làm phẳng” tinh tế và quyết định chất

lượng của mọi chip hiện đại. Không có CMP:

- Không

thể stacking 3D IC.

- Không

thể in lithography độ phân giải cao.

- Không

thể sản xuất vi mạch đa tầng BEOL chính xác.

Dù ít khi được nhắc đến, CMP là nền móng âm thầm đứng

sau mọi thành tựu vi mô của ngành bán dẫn.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận