Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

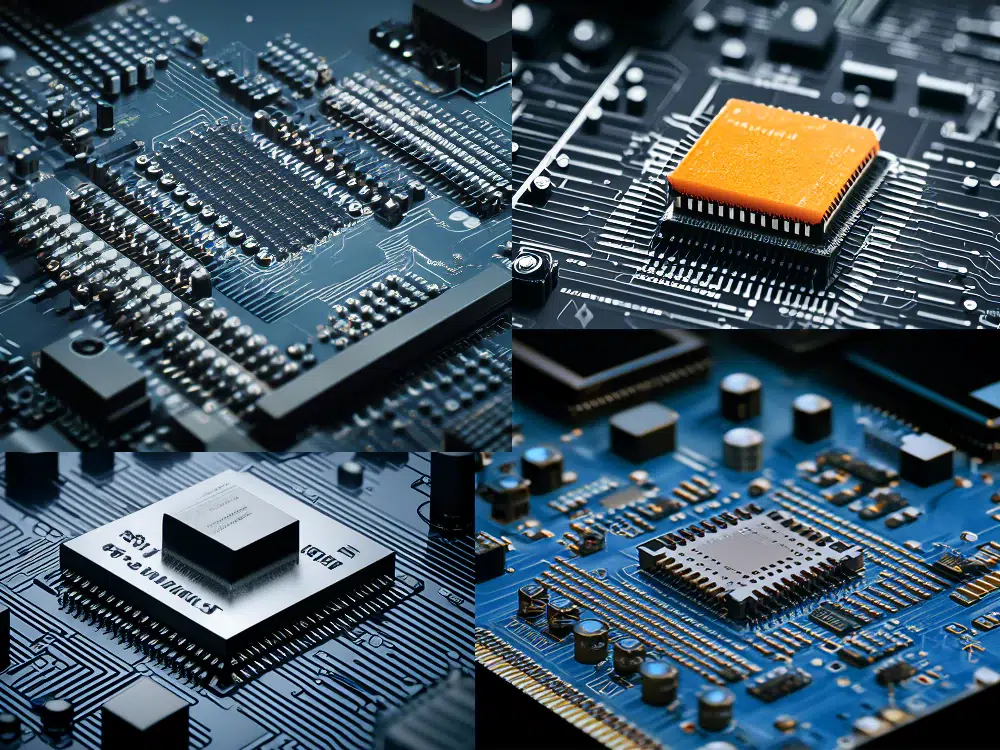

CHẾ TẠO & PACKAGING – BIẾN CÁT THÀNH BỘ NÃO ĐIỆN TỬ

Bạn có tin rằng cát – thứ tưởng chừng tầm thường nhất trên Trái Đất – lại chính là nguyên liệu tạo nên bộ não điện tử cho máy tính, điện thoại, xe tự lái, vệ tinh,...?

Hành trình kỳ diệu ấy bắt đầu từ silicon tinh khiết, nhưng chỉ khi trải qua hai giai đoạn quan trọng:

-

Chế tạo (Fabrication): Khắc mạch điện tử nano lên tấm wafer silicon

-

Đóng gói (Packaging): Bảo vệ và kết nối các die thành một con chip hoàn chỉnh

Hãy cùng IC Academy khám phá các bước chế tạo và đóng gói chip – một trong những kỳ tích công nghệ phức tạp nhất mà con người từng tạo ra.

CHẾ TẠO (FABRICATION): VŨ ĐIỆU NANO TRÊN SILICON

Toàn bộ quá trình bắt đầu từ wafer silicon tinh khiết, có đường kính phổ biến từ 200 – 300 mm. Trên mỗi tấm wafer, hàng trăm die (chip con) được tạo ra đồng thời.

Quy trình chế tạo bao gồm hàng trăm bước vi mô, trong đó có những bước nổi bật:

-

Oxidation: Phủ lớp oxide cách điện lên bề mặt

-

Photolithography: Dùng ánh sáng cực tím để in mẫu mạch siêu nhỏ

-

Etching: Ăn mòn lớp vật liệu không cần thiết theo mẫu đã in

-

Ion Implantation: Cấy tạp chất để thay đổi tính chất dẫn điện của silicon

-

Deposition: Phủ các lớp vật liệu dẫn điện và cách điện xen kẽ

-

CMP (Chemical Mechanical Planarization): Làm phẳng bề mặt sau mỗi lớp xử lý

Tổng cộng, một con chip hiện đại có thể gồm 50–100 lớp mạch điện tử siêu mỏng, mỗi lớp có độ dày chỉ bằng 1/1000 sợi tóc. Một sai sót nhỏ ở bất kỳ lớp nào đều có thể khiến toàn bộ die bị hỏng.

Khi hoàn tất, wafer sẽ được kiểm tra nghiêm ngặt, sau đó cắt (dicing) thành các die riêng biệt, chuẩn bị bước vào giai đoạn tiếp theo.

ĐÓNG GÓI (PACKAGING): BẢO VỆ & KẾT NỐI SỨC MẠNH CHIP

Dù mạnh mẽ, die sau khi chế tạo vẫn chỉ là những miếng silicon nhỏ bé, dễ vỡ. Để trở thành một con chip hoàn chỉnh, die cần được đóng gói (packaging) – công đoạn kết hợp khoa học vật liệu, điện tử và cơ khí chính xác.

Mục tiêu của Packaging bao gồm:

-

Bảo vệ die khỏi va chạm, nhiệt độ cao và độ ẩm

-

Kết nối điện giữa die và bo mạch ngoài qua các kỹ thuật nối (wire, bump…)

-

Tản nhiệt hiệu quả, giúp chip hoạt động ổn định ở hiệu suất cao

CÁC PHƯƠNG PHÁP ĐÓNG GÓI PHỔ BIẾN

Tùy thuộc vào hiệu năng, không gian, chi phí và mục đích sử dụng, các kỹ sư sẽ lựa chọn phương pháp đóng gói phù hợp. Một số kỹ thuật phổ biến bao gồm:

-

Wire Bonding: Dùng dây kim loại cực mảnh để nối die với chân chip

-

Flip Chip: Lật úp die và gắn trực tiếp lên đế bằng các bump siêu nhỏ

-

Fan-Out / Fan-In: Mở rộng hoặc thu gọn diện tích kết nối giúp tản nhiệt tốt hơn

-

System in Package (SiP): Gắn nhiều die vào cùng một gói, cho phép tạo thành module đa chức năng

-

3D Packaging / Chiplet: Xếp chồng hoặc ghép nhiều die theo chiều dọc, giúp tiết kiệm không gian và tăng hiệu năng

Các phương pháp đóng gói hiện đại không chỉ là yếu tố “đóng khung” cuối cùng, mà còn góp phần nâng tầm hiệu suất chip mà không cần thu nhỏ transistor.

TỪ CHIP ĐẾN ỨNG DỤNG TRONG CUỘC SỐNG

Sau khi đóng gói, con chip sẽ tiếp tục trải qua:

-

Kiểm tra cuối (Final Test) để đảm bảo chất lượng

-

Gắn nhãn, mã hóa để truy xuất nguồn gốc

-

Đóng vào reel hoặc tray và xuất xưởng

Những con chip này sẽ được sử dụng trong điện thoại thông minh, máy tính, ô tô, robot, vệ tinh, thiết bị IoT,… – góp phần tạo nên một thế giới công nghệ hiện đại và kết nối.

BẠN CÓ BIẾT?

-

Một nhà máy chế tạo chip hiện đại có thể cần đầu tư đến 20 tỷ USD

-

Công nghệ Advanced Packaging đang được xem như chìa khóa tiếp theo để tăng hiệu suất chip mà không cần giảm kích thước transistor

-

Chiplet – kỹ thuật ghép nhiều die – đang là xu hướng mới, được các ông lớn như AMD, Intel, Apple đẩy mạnh ứng dụng

ĐỪNG CHỈ ĐỌC – HÃY CÙNG BẮT ĐẦU

Chế tạo và đóng gói vi mạch không chỉ là khoa học, mà là một nghệ thuật tinh vi giữa kỹ thuật, vật lý và sự chính xác tuyệt đối.

IC Academy sẽ đồng hành cùng bạn – từng bước tìm hiểu, thực hành và sáng tạo – để mở cánh cửa bước vào ngành công nghiệp vi mạch. Đây không chỉ là tương lai của công nghệ, mà là nơi bạn thiết kế nên tương lai chính mình.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận