Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

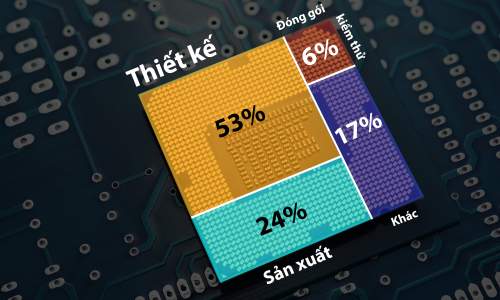

Các loại hình công việc chuyên môn trong ngành thiết kế và sản xuất vi mạch

Các công việc chuyên môn thường được yêu cầu trong ngành thiết kế và sản xuất vi mạch, có thể nhiều hơn hoặc ít hơn tùy từng dự án và từng công ty.

Viết và tối ưu hóa mã RTL cho các khối chức năng logic: Đây là bước viết mã mô tả mạch số ở cấp độ RTL, thể hiện logic của các khối chức năng trong hệ thống. Mục tiêu là tối ưu hóa để đáp ứng yêu cầu về hiệu năng, công suất và diện tích.

Thiết kế và tích hợp IP cores: Sử dụng các khối IP (Intellectual Property) đã được phát triển sẵn và tích hợp vào thiết kế tổng thể. Các IP có thể là CPU cores, memory controllers, hoặc các giao diện khác.

2. RTL Verification

Xác minh chức năng của thiết kế qua simulation và formal verification: Dùng các công cụ mô phỏng và kiểm chứng hình thức để đảm bảo thiết kế RTL đáp ứng đúng yêu cầu.

Phát triển testbench và các bài kiểm thử: Thiết kế testbench và viết các bài kiểm thử để xác minh các kịch bản hoạt động khác nhau của hệ thống.

3. FPGA Prototyping

Thiết kế, triển khai và thử nghiệm hệ thống trên FPGA: Dùng FPGA để mô phỏng thiết kế RTL trước khi chuyển sang giai đoạn sản xuất ASIC, giúp phát hiện sớm các lỗi tiềm ẩn và đánh giá hiệu năng thực tế.

4. Constraint Development

Phát triển các ràng buộc timing, hiệu năng, công suất: Định nghĩa các ràng buộc về timing, năng lượng tiêu thụ, diện tích để đảm bảo thiết kế đạt được các yêu cầu PPA (Performance, Power, Area).

5. Low Power Design

Thiết kế giảm tiêu thụ năng lượng: Tối ưu hóa các phần của thiết kế để giảm điện năng tiêu thụ mà vẫn giữ được hiệu năng cần thiết. Đưa vào các chế độ tiết kiệm điện năng khi hệ thống không hoạt động.

6. Design Space Exploration

Khám phá các tùy chọn thiết kế: Đánh giá và tối ưu hóa các phương án thiết kế khác nhau để tìm ra giải pháp tối ưu về PPA.

7. Clock Domain Crossing (CDC) Analysis

Phân tích CDC: Xử lý các vấn đề khi tín hiệu truyền qua các miền đồng hồ khác nhau, đảm bảo dữ liệu không bị mất hoặc xung đột trong hệ thống.

8. Multi-Voltage Design Implementation

Thiết kế hệ thống sử dụng nhiều mức điện áp: Tối ưu hóa việc sử dụng các mức điện áp khác nhau cho các thành phần trong hệ thống nhằm cải thiện hiệu suất và giảm tiêu thụ năng lượng.

9. Formal Verification

Kiểm chứng toán học: Sử dụng các công cụ kiểm chứng hình thức để đảm bảo tính chính xác của thiết kế mà không cần mô phỏng toàn bộ các trường hợp có thể xảy ra.

10. Design for Testability (DFT)

Thiết kế để dễ kiểm tra: Áp dụng các chiến lược như Scan Design, ATPG (Automatic Test Pattern Generation), và Memory BIST (Built-In Self-Test) để đảm bảo hệ thống dễ dàng được kiểm tra sau khi sản xuất.

11. Performance, Power, Area (PPA) Optimization

Tối ưu hóa PPA: Tối ưu hóa hiệu năng, công suất và diện tích trong thiết kế để đạt được sự cân bằng giữa các yếu tố này.

12. Clock Tree Synthesis (CTS)

Thiết kế cây phân phối đồng hồ: Tạo ra cây phân phối tín hiệu đồng hồ đồng đều tới tất cả các phần của hệ thống để đảm bảo mọi thành phần hoạt động đồng bộ.

13. Static Timing Analysis (STA)

Phân tích thời gian tĩnh: Kiểm tra xem thiết kế có đáp ứng được các yêu cầu về timing hay không mà không cần phải thực hiện mô phỏng đầy đủ.

14. Power Grid Design and Analysis

Thiết kế và phân tích lưới cấp nguồn: Đảm bảo lưới cấp nguồn có khả năng cung cấp đủ dòng điện cho toàn bộ thiết kế mà không gây ra các vấn đề như sụt áp (IR drop) hoặc nhiễu nguồn.

15. Signal Integrity Analysis

Phân tích tính toàn vẹn của tín hiệu: Kiểm tra và giảm thiểu các vấn đề liên quan đến nhiễu và biến dạng tín hiệu trên các kết nối tốc độ cao.

16. Cross-Talk Analysis

Phân tích xuyên nhiễu (cross-talk): Kiểm tra và giảm thiểu hiện tượng xuyên nhiễu giữa các đường tín hiệu để đảm bảo dữ liệu truyền qua mạch tích hợp không bị lỗi.

17. EMI/EMC Analysis (Electromagnetic Interference/Compatibility)

Phân tích nhiễu điện từ: Kiểm tra và giảm thiểu các vấn đề liên quan đến nhiễu điện từ (EMI), đảm bảo các hệ thống có thể hoạt động cùng nhau mà không gây nhiễu (EMC).

18. Physical Verification Simulation (DRC, LVS)

Kiểm tra DRC và LVS: Đảm bảo thiết kế đáp ứng các quy tắc sản xuất và layout đúng với sơ đồ mạch điện.

19. IP Integration and Verification

Tích hợp và xác minh IP: Tích hợp các IP cores vào thiết kế tổng thể và xác minh chúng hoạt động tương thích với các thành phần khác của hệ thống.

20. Tapeout and GDSII Finalization

Chuẩn bị GDSII cho tapeout: Chuẩn bị các tệp GDSII và kiểm tra kỹ lưỡng trước khi gửi thiết kế đi sản xuất tại nhà máy đúc (foundry).

21. Yield Optimization

Tối ưu hóa tỷ lệ sản xuất: Phân tích và giảm thiểu các lỗi sản xuất để tối ưu hóa tỷ lệ yield, đảm bảo sản xuất ra số lượng chip đạt chuẩn cao nhất.

22. Reliability Analysis

Phân tích độ tin cậy: Xác định các vấn đề như di chuyển electron (electromigration), nhiệt độ hoạt động và kiểm tra độ tin cậy của thiết kế qua các mô phỏng.

23. Post-Silicon Validation

Kiểm tra sau sản xuất: Kiểm tra chip sau khi được sản xuất, đảm bảo chức năng và hiệu năng thực tế đúng với dự đoán mô phỏng.

24. Embedded Software Development for SoC

Phát triển phần mềm nhúng cho SoC: Phát triển và kiểm thử phần mềm nhúng tương thích với hệ thống trên chip (SoC), đảm bảo sự phối hợp giữa phần cứng và phần mềm.

Quy trình trên thể hiện từng bước của quá trình thiết kế và tối ưu hóa một con chip, từ giai đoạn thiết kế logic RTL cho đến sản xuất và kiểm tra sau silicon.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận