Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

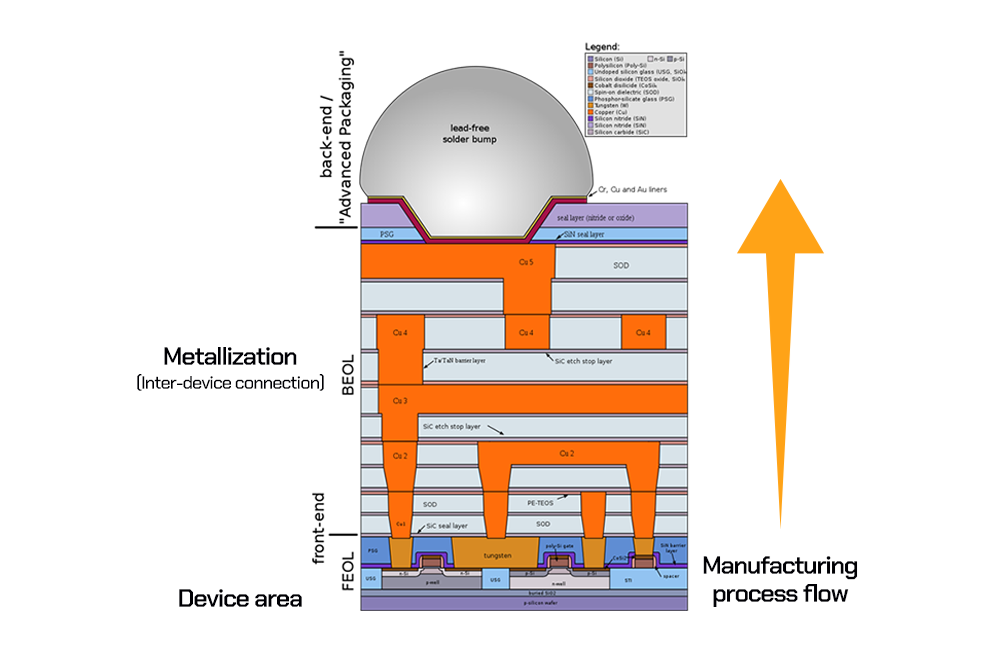

BEOL – Dây dẫn của chip hiện đại

Bạn đã có hàng tỷ transistor từ giai đoạn FEOL?

Tuyệt vời. Nhưng nếu các transistor đó không được kết nối, thì con chip

vẫn vô dụng. Đó chính là lúc Backend of Line (BEOL) xuất hiện – giai đoạn

xây dựng hệ thống liên kết kim loại nhiều tầng để tạo thành vi mạch

hoàn chỉnh.

BEOL là

gì?

Backend of Line (BEOL) là giai đoạn hậu kỳ

trong quá trình chế tạo chip. Ở đây, người ta tiến hành kết nối các

transistor đã được hình thành trong FEOL bằng cách khắc và đắp các lớp

kim loại siêu mỏng, tạo nên mạng lưới logic, nguồn và tín hiệu trên bề mặt

silicon die.

Nếu FEOL là nơi transistor ra đời, thì BEOL là nơi

những transistor đó “trò chuyện” và phối hợp thành hệ thống vi mạch thực sự.

BEOL gồm

những gì?

1. Metal Layers – Các lớp kim loại siêu mỏng, thường

là đồng (Cu) hoặc nhôm (Al). Chúng được đánh số từ M1 (lớp thấp)

đến M10+ (lớp cao) tùy theo độ phức tạp của chip.

2. Dielectric (ILD) – Vật liệu cách điện giữa các

tầng kim loại, như SiO₂, Low-k hay Ultra

Low-k để giảm điện dung ký sinh.

3. Via – Những cột nối dọc giữa các lớp metal,

như các thang máy siêu nhỏ dẫn tín hiệu xuyên tầng.

4. Contact – Các tiếp điểm nối từ transistor

(FEOL) lên tầng kim loại đầu tiên (M1).

5. CMP (Chemical Mechanical Planarization) – Quá

trình làm phẳng từng lớp, đảm bảo bề mặt không gồ ghề để có thể tiếp tục

khắc chính xác ở các tầng sau.

BEOL để

làm gì?

- Kết

nối logic: Nối các cổng NAND, NOR, XOR… lại để tạo thành mạch số hoàn

chỉnh.

- Định

tuyến tín hiệu: Truyền dữ liệu giữa các khối logic, bộ nhớ, và các IP

khác trong chip.

- Phân

phối nguồn: Tạo hệ thống cấp nguồn và tín hiệu đồng hồ ổn định đến

toàn chip.

- Liên

kết ngoại vi: Kết nối đến IO pads hoặc bump balls để

giao tiếp với bo mạch ngoài.

Một ví dụ

nhỏ:

Bạn thiết kế một vi xử lý có 12 tầng metal.

- M1

– M3 được dùng để nối logic chi tiết: các phép tính, điều kiện, nhảy lệnh.

- M4

– M6 định tuyến các bus dữ liệu, address bus, và các tín hiệu điều khiển.

- M7

– M9 tạo mạng lưới cấp nguồn.

- M10

– M12 chuyên chở xung nhịp (clock), tín hiệu I/O hoặc là bus hệ thống

tốc độ cao.

Chỉ cần 1 via bị thiếu hoặc short → tín hiệu clock

không đến → toàn bộ logic hoạt động sai → chip hỏng dù transistor vẫn đúng → BEOL

fail = chip fail.

Những

công nghệ gắn liền với BEOL:

- Dual

Damascene – Kỹ thuật khắc via và trench trong một quy trình duy

nhất, tối ưu số bước.

- Cu

CMP – Mạ đồng và đánh bóng để tạo dây mạch phẳng mịn, giảm điện trở và

đảm bảo độ chính xác.

- Low-k

/ Ultra Low-k Dielectric – Giảm điện dung giữa dây, tăng tốc độ và giảm

công suất tiêu thụ.

- Air-Gap

Isolation – Thay vì điền vật liệu giữa dây, tạo khoảng trống không

khí để giảm tương tác điện.

- EUV

Lithography – Sử dụng tia cực tím bước sóng cực nhỏ để in các dây

siêu mảnh, cỡ dưới 20nm.

Những lưu

ý quan trọng khi thiết kế và chế tạo BEOL:

- Khoảng

cách giữa dây cực nhỏ → rất dễ xảy ra short (nối tắt) hoặc open

(đứt mạch) nếu lệch 1–2 nm.

- Nhiều

lớp metal gây ứng suất → có thể cong die hoặc gây nứt ở nhiệt độ

cao.

- Tản

nhiệt yếu → nếu power grid không thiết kế tối ưu, chip có thể nóng

cục bộ, giảm tuổi thọ.

- Không

thể sửa lỗi BEOL sau khi hoàn tất → dù phần transistor bên dưới đúng,

lỗi BEOL = toàn chip vô dụng.

Vì sao

BEOL ngày càng khó?

- Khi

tiến đến node công nghệ nhỏ hơn (5nm, 3nm), chiều rộng dây và

khoảng cách via chỉ còn vài chục nanomet.

- Việc

đảm bảo không có lỗi trong hàng tỷ kết nối là một thách thức cực

lớn về kỹ thuật, vật liệu và môi trường.

- Mỗi lớp

metal thêm vào làm tăng chi phí, thời gian và độ phức tạp sản xuất.

Kết luận:

BEOL chính là “mạch máu” nuôi sống hệ thần kinh của

con chip.

Nếu transistor là tế bào, thì chính các dây nối trong BEOL cho phép các

tế bào đó tương tác, truyền tín hiệu và làm việc như một khối thống nhất.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận