Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

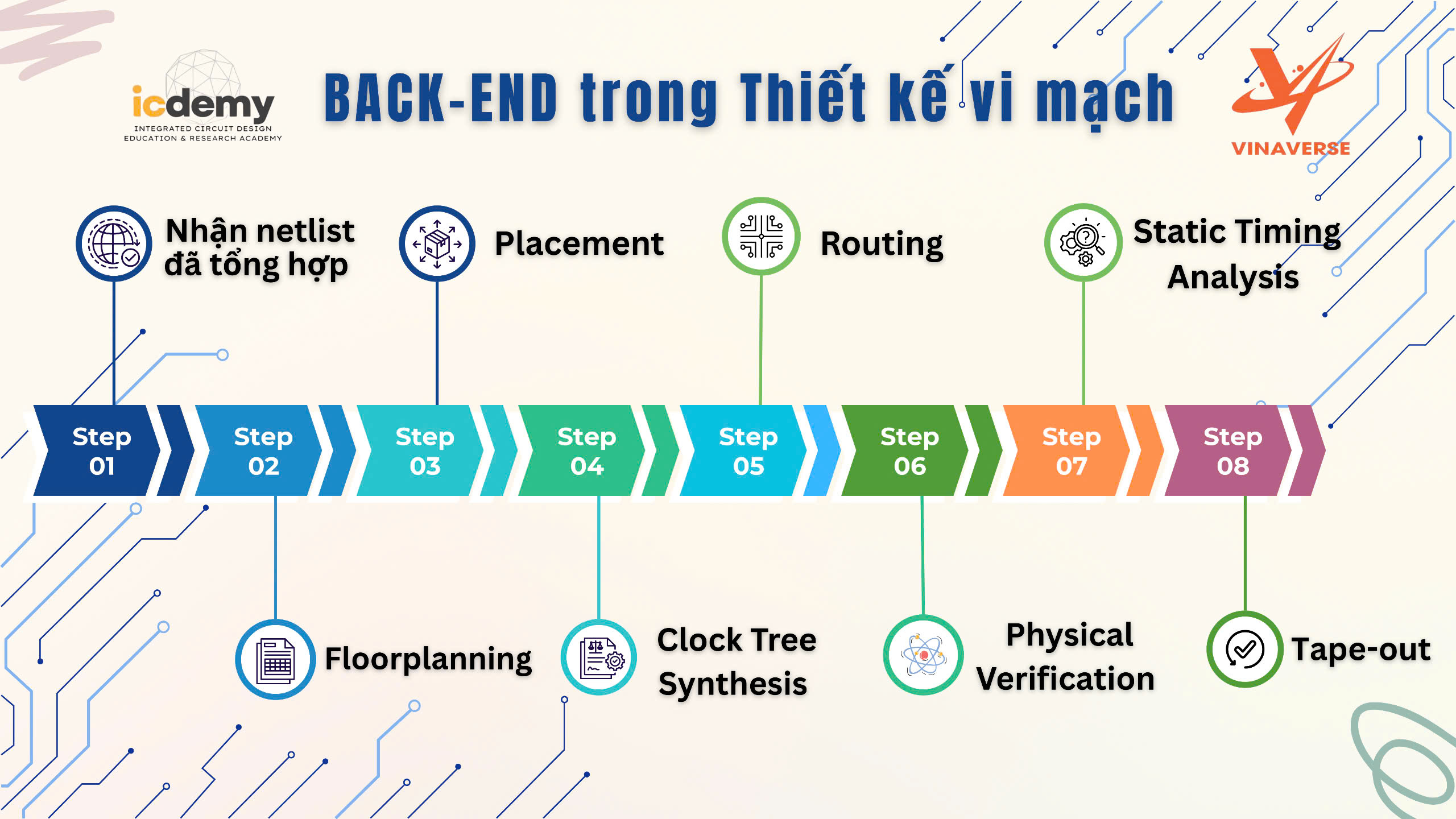

Back-End trong Thiết kế Vi Mạch – Hành Trình Từ Netlist Đến Silicon

Trong thế giới thiết kế vi mạch (IC Design), Front-End là nơi các kỹ sư tạo nên hành vi logic của mạch bằng các ngôn ngữ như Verilog hay VHDL. Tuy nhiên, một con chip không thể đi vào sản xuất chỉ với những dòng mã RTL – cần phải có một quá trình chuyển hóa toàn bộ thiết kế thành hiện thực vật lý. Đó chính là vai trò của Back-End – nơi mọi thứ được hiện thực hóa bằng transistor, kim loại và dòng điện.

Back-End là gì?

Back-End là quy trình triển khai vật lý từ netlist đã tổng hợp (Gate-Level Netlist), nhằm chuyển nó thành một layout hoàn chỉnh sẵn sàng cho chế tạo silicon thực tế – còn gọi là tape-out.

Các bước chính trong quy trình Back-End

1. Nhận Netlist đã tổng hợp

Quá trình bắt đầu khi thiết kế RTL được chuyển thành netlist ở cấp cổng – mô tả mạch bằng các phần tử như AND, OR, flip-flop từ thư viện standard cell. Netlist này là nguyên liệu đầu vào cho quy trình Back-End.

2. Floorplanning – Quy hoạch sơ đồ chip

Kỹ sư xác định:

-

Kích thước vùng core

-

Vị trí các IP lớn (SRAM, PLL…)

-

Vùng I/O và hệ thống cấp nguồn (power ring, power strap)

Quy hoạch tốt giúp tránh nghẽn tín hiệu và hỗ trợ các bước sau hiệu quả hơn.

3. Placement – Sắp xếp cell

Hàng trăm nghìn đến hàng triệu cell logic được công cụ EDA tự động sắp xếp vào vùng core sao cho tối ưu về diện tích và độ dài dây. Kỹ sư sẽ bổ sung:

-

Filler cell để lấp khoảng trống

-

Tap cell để ổn định điện thế, tránh latch-up

4. Clock Tree Synthesis – Tổng hợp cây xung clock (CTS)

Xây dựng mạng phân phối clock đồng đều đến các flip-flop nhằm giảm skew và insertion delay. Kỹ sư sẽ:

-

Chèn buffer/inverter

-

Áp dụng cấu trúc H-tree hoặc balanced tree

5. Routing – Định tuyến dây kết nối

Routing bao gồm:

-

Global routing: định hướng sơ bộ

-

Detailed routing: vẽ dây thật trên các lớp kim loại, tuân thủ:

-

Khoảng cách dây

-

Chiều rộng

-

Số lượng via

-

Clock và reset thường được ưu tiên ở các lớp kim loại cao hơn để giảm nhiễu.

6. Physical Verification – Kiểm tra vật lý

Đây là bước "soi lỗi" toàn diện trước khi tape-out:

-

DRC: Kiểm tra quy tắc thiết kế theo yêu cầu của fab

-

LVS: So sánh layout với sơ đồ logic (netlist)

-

Kiểm tra antenna effect, thêm diode bảo vệ nếu cần

7. Static Timing Analysis – Phân tích thời gian tĩnh (STA)

Sử dụng công cụ như PrimeTime hoặc Tempus để đánh giá tín hiệu có bị vi phạm setup/hold không. Nếu có lỗi timing:

-

Chỉnh sửa đường truyền

-

Áp dụng ECO (Engineering Change Order) để sửa logic mà không ảnh hưởng đến layout tổng thể

8. Tape-out – Hoàn tất gửi đi chế tạo

Khi toàn bộ các kiểm tra như DRC, LVS, STA, IR drop, EM... đều đạt yêu cầu, thiết kế sẽ được tape-out – tức là gửi layout đi chế tạo mask. File layout sẽ được xuất ra định dạng GDSII hoặc OASIS và nộp cho xưởng đúc để sản xuất chip thật. Đây là khoảnh khắc quan trọng, kết tinh toàn bộ nỗ lực của nhóm kỹ sư Back-End.

Kết luận

Back-End chính là nơi biến những mô tả logic thành hiện thực vật lý – là cầu nối giữa thế giới ảo và con chip thật. Mỗi bước đi trong hành trình này đều đòi hỏi độ chính xác cao, sự phối hợp chặt chẽ giữa con người và công cụ EDA.

Hành trình từ Netlist đến Silicon không chỉ là kỹ thuật, mà còn là nghệ thuật trong việc hiện thực hóa giấc mơ công nghệ.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận