Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

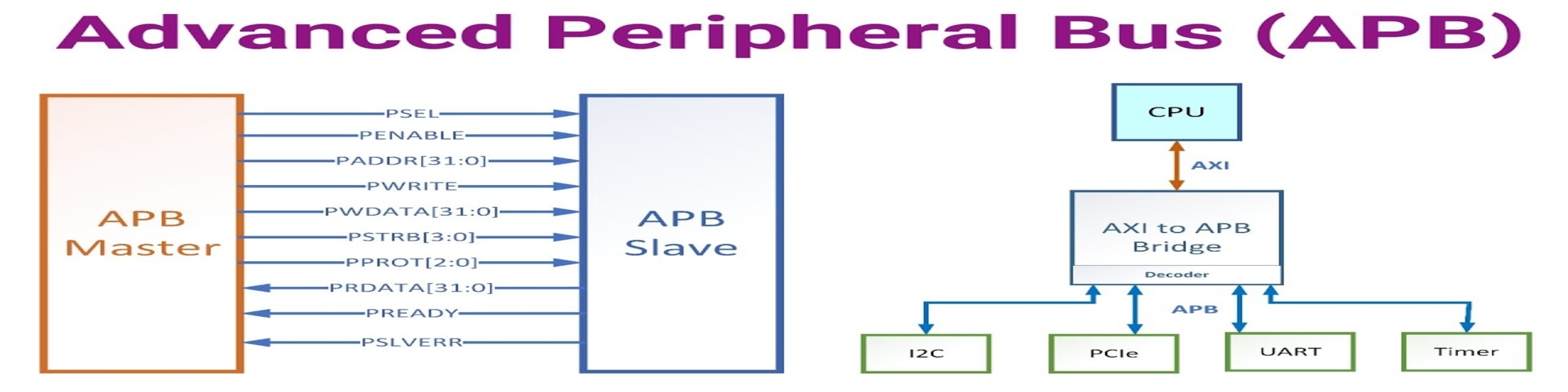

APB Protocol – Hiểu và Kiểm Chứng Từ A đến Z

Trong thiết kế SoC (System-on-Chip), các bus

protocol đóng vai trò cực kỳ quan trọng trong việc kết nối giữa CPU

và các thiết bị ngoại vi (peripherals). Bên cạnh những giao thức phức tạp

như AXI hay AHB, có một giao thức đơn giản nhưng thiết yếu là APB

(Advanced Peripheral Bus) – thuộc chuẩn AMBA do ARM đề xuất.

APB được sử dụng rộng rãi trong các thiết kế công nghiệp bởi

tính chất đơn giản, tiết kiệm công suất và dễ triển khai. Bài viết này sẽ

phân tích từ khái niệm, cấu trúc tín hiệu, cơ chế truyền dữ liệu,

đến quy trình kiểm chứng (Verification) trong DV (Design Verification).

1. APB là

gì?

APB (Advanced Peripheral Bus) là một giao thức bus

thuộc chuẩn AMBA (Advanced Microcontroller Bus Architecture). Mục đích của

APB là phục vụ giao tiếp với các thiết bị ngoại vi tốc độ thấp, ví dụ: Timer,

UART, GPIO, I2C, SPI, Watchdog…

Một số đặc điểm chính của APB:

- Thiết

kế đơn giản: Không có pipeline phức tạp như AXI hoặc burst như AHB.

- Tiêu

tốn ít công suất: Do giao dịch chỉ diễn ra trong 2 pha (Setup và

Enable).

- Cấu

trúc Master – Slave:

- Master

thường là một Bridge từ AHB/AXI.

- Slave

chính là các peripheral (UART, GPIO...).

Với đặc tính này, APB thường được dùng trong tầng ngoại vi

(peripheral layer) của hệ thống SoC.

2. Các

tín hiệu chính trong APB

Một giao tiếp APB bao gồm các tín hiệu điều khiển, địa chỉ

và dữ liệu. Những tín hiệu quan trọng nhất bao gồm:

- PCLK:

Clock của hệ thống APB.

- PRESETn:

Reset, active-low.

- PADDR:

Bus địa chỉ, xác định thanh ghi (register) cần truy cập.

- PWDATA:

Dữ liệu được ghi từ Master sang Slave.

- PRDATA:

Dữ liệu được đọc từ Slave về Master.

- PWRITE:

Tín hiệu điều khiển ghi (1) hoặc đọc (0).

- PSEL:

Chọn slave đích trong nhiều peripheral.

- PENABLE:

Tín hiệu điều khiển pha Enable.

- PREADY:

Slave báo hiệu đã sẵn sàng.

- PSLVERR:

Slave báo lỗi (error).

Mỗi tín hiệu trên đóng vai trò then chốt trong việc xác định

đúng địa chỉ, đúng dữ liệu và đảm bảo việc truyền nhận diễn ra theo chuẩn

timing.

3. Cơ chế

truyền dữ liệu trong APB

Một giao dịch APB được chia thành 2 pha chính:

Setup Phase

- Master

phát PADDR, PWRITE, PWDATA, PSEL.

- PENABLE

= 0.

Enable Phase

- Master

set PENABLE = 1.

- Nếu PREADY

= 1, giao dịch kết thúc thành công.

- Nếu PREADY

= 0, Master giữ trạng thái và chờ cho đến khi Slave sẵn sàng.

→ Mỗi transaction tối thiểu 2 chu kỳ clock (1 chu kỳ

Setup, 1 chu kỳ Enable).

Điều này làm cho APB trở thành một giao thức không tối ưu

về throughput, nhưng đơn giản và tiết kiệm năng lượng, phù hợp cho

ngoại vi.

4. Ví dụ

giao dịch APB

Giao dịch đọc

- Setup

phase: Master đưa địa chỉ cần đọc lên PADDR, set PWRITE = 0,

chọn slave bằng PSEL.

- Enable

phase: Master bật PENABLE = 1, Slave trả về dữ liệu qua PRDATA.

Giao dịch ghi

- Setup

phase: Master đưa PADDR, PWDATA, set PWRITE = 1, chọn

slave bằng PSEL.

- Enable

phase: Master bật PENABLE = 1, Slave nhận dữ liệu từ PWDATA.

Trong cả hai trường hợp, nếu PREADY = 0, giao dịch bị

kéo dài cho đến khi Slave sẵn sàng.

5.

Verification APB Slave

Trong Design Verification (DV), việc kiểm chứng một APB

Slave (ví dụ: UART, GPIO) là rất quan trọng. Các yếu tố cần được xác minh

bao gồm:

- Đúng

địa chỉ – đúng dữ liệu: Khi ghi/đọc, dữ liệu phải được lưu/trả về

chính xác tại địa chỉ tương ứng.

- Xử

lý PREADY delay: Slave có thể chưa sẵn sàng ngay lập tức, do đó phải

kiểm tra việc Master chờ đợi đúng chuẩn.

- PSLVERR:

Khi có lỗi, Slave cần trả về tín hiệu báo lỗi đúng thời điểm.

- Tuân

thủ timing: Setup phase phải luôn trước Enable phase, không được vi phạm

quy tắc.

Thành phần cơ bản của Testbench APB:

- Driver:

Sinh ra stimulus (PADDR, PWDATA, PWRITE…) theo giao thức APB.

- Monitor:

Quan sát tín hiệu bus để đảm bảo tính đúng đắn và kiểm tra thời gian.

- Scoreboard:

So sánh dữ liệu thực tế (PRDATA) với dữ liệu kỳ vọng (expected model).

Nhờ có testbench này, DV engineer có thể phát hiện sớm các

bug liên quan đến địa chỉ sai, dữ liệu sai, timing lỗi, hoặc xử lý tín hiệu

bất thường.

6. Ý

nghĩa của APB trong DV

APB không chỉ là một giao thức thực tế trong SoC mà còn có ý

nghĩa lớn trong Design Verification:

- Là giao

thức nền tảng giúp DV engineer làm quen trước khi tiếp cận AHB/AXI – vốn

phức tạp hơn nhiều.

- Kiểm

chứng APB giúp engineer rèn luyện khả năng viết testbench chuẩn hóa,

từ đó mở rộng ra những bus protocol phức tạp.

- Trong

phỏng vấn DV, các câu hỏi về APB transaction, APB timing, hoặc

cách verify APB slave là rất phổ biến.

Kết luận

APB Protocol là một trong những giao thức cơ bản

nhưng cực kỳ quan trọng trong thiết kế SoC. Với cấu trúc đơn giản, ít

tiêu tốn công suất, APB phù hợp để kết nối CPU với các thiết bị ngoại vi

tốc độ thấp.

Trong Design Verification, việc hiểu rõ cơ chế hoạt

động, các tín hiệu chính, và phương pháp kiểm chứng APB Slave

giúp DV engineer phát hiện bug sớm, đảm bảo tính đúng đắn của thiết kế.

APB có thể coi là bước khởi đầu quan trọng trên hành

trình nắm vững các bus protocol của AMBA, đồng thời là nền tảng không thể thiếu

trước khi tiến lên AHB và AXI.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận