Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

ANTENNA EFFECT – KHI TÍN HIỆU CHƯA KỊP VỀ, TRANSISTOR ĐÃ CHÁY

Bạn vừa hoàn tất layout cho một khối mạch logic phức tạp. Từng đường đi của tín hiệu đều được cân nhắc kỹ lưỡng, từng cell logic được bố trí hợp lý để tối ưu delay. Thiết kế đã pass hầu hết các check DRC. Bạn tin tưởng rằng mọi thứ đã sẵn sàng để tiến tới tape-out.

Nhưng rồi, một lỗi “lạ” xuất hiện trong quá trình signoff: Antenna Violation.

Bạn bối rối: “Mình đâu có thiết kế ăng-ten nào trên con chip này?”

Sự thật là: chính bạn đã vô tình tạo ra một chiếc “ăng-ten” gây hại, chỉ bằng cách route dây chưa hợp lý trong quá trình layout!

Antenna Effect là gì?

Antenna Effect là một hiện tượng xảy ra trong giai đoạn fabrication (sản xuất) chip, khi các đoạn dây kim loại được hình thành nhưng chưa kết nối hoàn chỉnh với transistor. Trong thời gian “chờ” đó, đoạn dây có thể tích tụ điện tích từ plasma hoặc từ môi trường xử lý, giống như một ăng-ten nhỏ thu tĩnh điện.

Khi lượng điện tích tích tụ đủ lớn, nó tạo ra một điện áp cao bất thường trên gate transistor, đủ để phá vỡ lớp oxide mỏng (gate oxide breakdown) – và kết quả là transistor bị hỏng vĩnh viễn, ngay cả khi con chip chưa hoạt động lần nào.

Vì sao Antenna Effect nguy hiểm?

Điều khiến Antenna Effect nguy hiểm nằm ở chỗ: nó không xuất hiện trong schematic, không thể phát hiện qua simulation hoặc waveform. Bạn chỉ có thể thấy nó sau khi layout xong, khi chạy các công cụ signoff chuyên dụng như Calibre, IC Validator, v.v.

Hơn nữa, lỗi này thường không gây ảnh hưởng đến toàn bộ chip, mà chỉ làm hỏng một số gate transistor nằm trong các net nhạy cảm – như tín hiệu clock, reset, enable – gây ra lỗi “random” rất khó truy tìm khi debug.

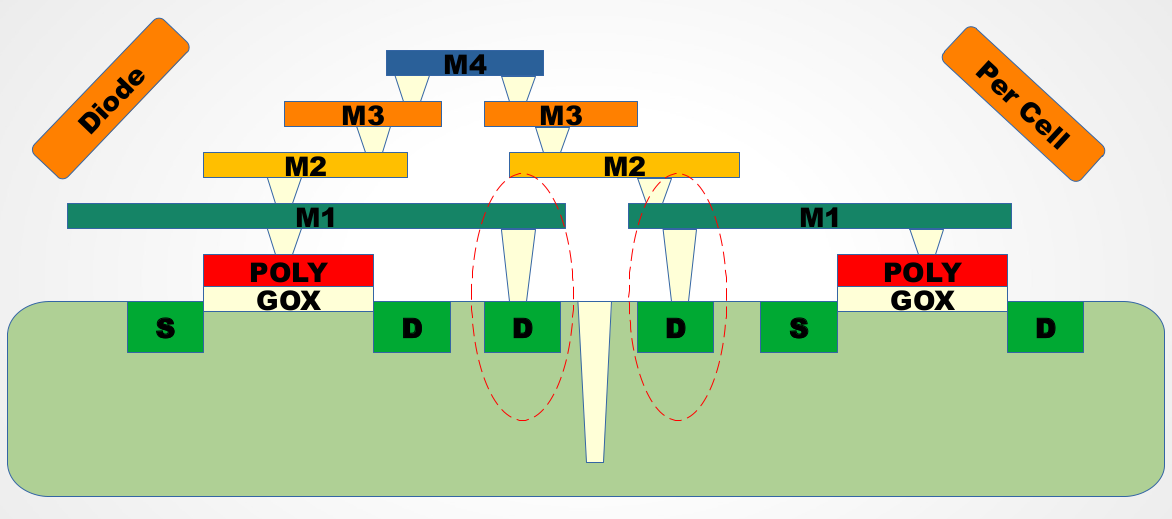

Cơ chế hình thành Antenna Effect

Trong quá trình fabrication, chip được xây dựng từ dưới lên – bắt đầu từ transistor, rồi tới các lớp dây kim loại (metal layers) như M1, M2, M3…

Tuy nhiên, một số phần của dây kim loại có thể được khắc xong trước khi kết nối tới transistor ở lớp dưới cùng hoàn tất. Trong thời gian đó:

-

Các đoạn dây này hoạt động như một "antenna" thu điện tích từ plasma etching (quá trình làm sạch bằng plasma).

-

Do chưa có đường thoát (vì chưa nối xuống transistor), lượng điện tích này dồn vào gate.

-

Gate oxide mỏng, chỉ dày vài nm, dễ dàng bị đánh thủng bởi điện áp tích tụ.

-

Kết quả: gate hỏng vĩnh viễn, transistor không hoạt động, mạch lỗi hoàn toàn.

Khi nào hiện tượng này dễ xảy ra?

Các tình huống điển hình dễ phát sinh Antenna Effect gồm:

-

Net có nhiều branch, dây dài, đặc biệt là các tín hiệu phân phối như clock, reset, enable.

-

Dây đi ở các metal layer cao (M3, M4, M5…) nhưng không có via xuống lớp thấp để sớm nối với transistor.

-

Tín hiệu đi đến nhiều module, trong khi phần nối xuống gate transistor lại được hoàn tất ở bước routing sau cùng.

-

Tỷ lệ diện tích dây (metal area) so với diện tích gate quá lớn, vượt ngưỡng cho phép của PDK.

Một ví dụ điển hình

Bạn có một tín hiệu RESET, cần phân phối đến 10 module khác nhau. Trong quá trình route, công cụ tạo ra một mạng dây phân nhánh lớn, sử dụng các lớp metal cao như M4.

Tuy nhiên, phần gate nhận tín hiệu RESET lại nằm ở một vùng xa, chỉ được nối xuống sau cùng bằng một via nhỏ từ M1.

Khi fabrication diễn ra:

-

Các phần dây RESET đã hình thành, nhưng chưa nối xuống transistor.

-

Trong lúc đó, đoạn dây này bị plasma “nạp” điện tích → tích tụ tại gate.

-

Gate oxide chịu không nổi áp lực này → bị đánh thủng.

-

Và thế là, tín hiệu reset không hoạt động – chip lỗi mà không ai ngờ được lý do.

Cách phát hiện và khắc phục Antenna Effect

Rất may, Antenna Effect hoàn toàn có thể được phát hiện và xử lý nếu bạn tuân thủ đúng quy trình signoff.

1. Phát hiện:

-

Sử dụng các công cụ layout verification như Calibre, IC Validator, PVS...

-

Kiểm tra các rule liên quan tới antenna ratio – tỷ lệ diện tích kim loại so với diện tích gate.

-

Chạy check antenna violation trước khi tape-out.

2. Khắc phục:

-

Thêm antenna diode: Diode nối từ net nhạy cảm xuống GND giúp xả điện tích an toàn.

-

Sắp xếp routing khéo léo: Bố trí sao cho phần nối xuống gate được hình thành sớm, tránh dây “bị lẻ loi”.

-

Chia nhỏ đoạn dây dài: Dùng các đoạn jump metal, hoặc chia segment bằng via và cut layer.

-

Tối ưu sơ đồ fanout: Tránh các mạng phân nhánh lớn không cần thiết, đặc biệt với tín hiệu nhạy cảm.

Kết luận

Antenna Effect là một trong những “kẻ thù vô hình” trong thiết kế layout IC. Dù bạn có logic đúng, timing đẹp, schematic sạch, nhưng nếu layout tạo ra các đoạn dây có khả năng tích tụ điện mà không có đường thoát, transistor của bạn có thể “hy sinh trong im lặng”.

Vì vậy, hãy luôn nhớ:

-

Dây tín hiệu không chỉ là đường truyền – nó có thể là “bẫy điện” nếu không được nối đúng lúc.

-

Thiết kế layout cũng giống như xây cầu – đừng căng dây điện nếu chưa nối hai đầu an toàn.

Bạn đã từng gặp antenna violation trong dự án thực tế chưa? Bạn xử lý nó như thế nào – diode, chỉnh route, hay phải làm lại cả đoạn mạch?

Thẻ:

AntennaEffect ICDesignTips PhysicalDesign ESDprotection HocICcungICdemy thiết kế vi mạch iCdemy0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận