Những hành trình đầy cảm hứng

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

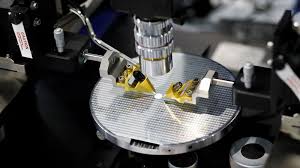

Alphawave Semi Đột Phá Với Công Nghệ UCIe 36G Trên TSMC 2nm

Ngành bán dẫn đang bước vào một giai đoạn chuyển mình mạnh

mẽ, nơi AI và kiến trúc chiplet trở thành trung tâm của đổi mới. Trong bối cảnh

đó, Alphawave Semi, công ty chuyên về kết nối tốc độ cao, vừa công bố một cột mốc

mang tính đột phá: tape-out thành công UCIe™ IP 36G trên tiến trình 2nm của

TSMC. Đây không chỉ là một thành tựu kỹ thuật, mà còn là dấu hiệu mở đường cho tương

lai AI hiệu năng cao và tiết kiệm năng lượng.

1.

UCIe 36G: Tăng Tốc Kết Nối Die-to-Die

UCIe 36G là chuẩn kết nối Universal Chiplet Interconnect

Express thế hệ mới, đạt tốc độ truyền 36Gbps giữa các die trong cùng một hệ thống.

Giải pháp này được xây dựng trên tiến trình 2nm của TSMC, sử dụng công nghệ nanosheet

transistor – một bước tiến vượt bậc so với FinFET.

Điểm đáng chú ý là mật độ băng thông lên tới 11.8 Tbps/mm,

cho phép xử lý khối lượng dữ liệu lớn với độ trễ thấp. Bên cạnh đó, sự kết hợp

với công nghệ đóng gói tiên tiến CoWoS® giúp tối ưu hóa việc tích hợp nhiều

chiplet trong cùng một package.

UCIe 36G không chỉ nhanh mà còn tiết kiệm điện năng, đặc

biệt phù hợp cho các hệ thống AI thế hệ mới, data center và high-performance

computing (HPC). Alphawave Semi cũng đã lên kế hoạch phát triển tiếp theo với UCIe

64G, mở ra khả năng kết nối băng thông cao gấp đôi trong tương lai gần.

2.

Vai Trò Trong Hệ Sinh Thái Chiplet

Thành công của UCIe 36G không chỉ là chiến thắng kỹ thuật

đơn lẻ. Nó còn là đòn bẩy chiến lược cho hệ sinh thái chiplet mở – một xu hướng

đang phát triển nhanh chóng nhằm thay thế các SoC monolithic truyền thống.

UCIe hỗ trợ nhiều giao thức tiêu chuẩn như PCIe, CXL, AXI,

cho phép các nhà phát triển dễ dàng tích hợp các chiplet từ các nhà cung cấp

khác nhau trong cùng một hệ thống. Điều này tăng tính linh hoạt trong thiết kế

và rút ngắn thời gian ra thị trường.

Ngoài ra, tính năng giám sát trực tiếp chất lượng truyền

tín hiệu giữa các die giúp nâng cao độ tin cậy, đảm bảo hiệu năng ổn định trong

các hệ thống AI có yêu cầu cao về tính chính xác và độ ổn định.

3.

Lợi Thế Của Công Nghệ 2nm Với Nanosheet

Tiến trình 2nm của TSMC là một bước tiến công nghệ lớn, sử

dụng transistor nanosheet (gate-all-around) để cải thiện kiểm soát dòng điện và

giảm tiêu thụ năng lượng. Đây là công nghệ cho phép các hệ thống AI chạy nhanh

hơn nhưng vẫn tiết kiệm điện – một điều kiện sống còn trong các trung tâm dữ liệu

và thiết bị edge.

Alphawave Semi đã khéo léo tận dụng đặc điểm này để tối

đa hóa hiệu suất của UCIe 36G, đồng thời đảm bảo khả năng mở rộng trong các thiết

kế chiplet thế hệ tiếp theo.

4.

Tương Lai AI Và Vai Trò Tiên Phong Của Alphawave Semi

Việc kết hợp UCIe 36G, tiến trình 2nm và công nghệ đóng

gói CoWoS đang giúp Alphawave Semi định hình lại cách thức xây dựng hệ thống AI

trong tương lai. Các cụm xử lý AI quy mô lớn – nơi nhiều chiplet cùng hoạt động

trong một thể thống nhất – đang trở nên khả thi hơn bao giờ hết.

Alphawave Semi đang không ngừng hợp tác với TSMC và nhiều

đối tác trong ngành để thúc đẩy chuẩn UCIe trở thành giao thức kết nối tiêu chuẩn

toàn cầu. Điều này sẽ mang lại lợi ích to lớn cho các nhà phát triển phần cứng,

đặc biệt trong bối cảnh nhu cầu AI tăng cao và yêu cầu về hiệu năng ngày càng

khắt khe.

5.

Kết Luận: Bước Đệm Cho Tương Lai Chiplet + AI

Với tape-out thành công UCIe 36G, Alphawave Semi đã ghi dấu

ấn mạnh mẽ trong cuộc đua chiplet. Đây là minh chứng rõ ràng cho tầm nhìn dài hạn

của họ – xây dựng các giải pháp kết nối mở, tốc độ cao, tiêu thụ điện thấp, phục

vụ cho AI và HPC thế hệ kế tiếp.

Công nghệ này không chỉ mang tính bước ngoặt trong kỹ thuật,

mà còn là nền tảng cho một thế giới AI mở – nhanh hơn, mạnh hơn và linh hoạt

hơn.

Hãy cùng đón chờ các bước tiến tiếp theo và tìm hiểu thêm tại ICdemy và Vinaverse

– nơi kết nối cộng đồng học công nghệ bán dẫn Việt Nam.

0 Bình luận

Danh mục

- 3. Kỹ thuật và công cụ thiết kế 103

- 1. Công nghệ vi mạch 60

- 5. Tin tức, Sự kiện và Tuyển dụng 15

- 4. Cộng đồng vi mạch 3

Bài viết gần đây

Logic Gate – Viên Gạch Đầu Tiên Của Mọi Bộ Vi Xử Lý

Mon, 15 Dec 2025

Để lại bình luận