Netlist – 'Bản đồ mạch điện' giúp chip đi từ ý tưởng đến thực tế

Sat, 19 Jul 2025

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

Trong lĩnh vực thiết kế vi mạch số, đặc biệt là mảng Design

Verification (DV), việc đảm bảo rằng một hệ thống hoạt động đúng chức năng là

nhiệm vụ then chốt. Để thực hiện điều đó, các kỹ sư Verification thường sử dụng

UVM – viết tắt của Universal Verification Methodology, một phương pháp

luận được tiêu chuẩn hóa và sử dụng rộng rãi trong công nghiệp vi mạch.

Một trong những thành phần cốt lõi khi áp dụng UVM là UVM

Testbench – nơi tập hợp toàn bộ hệ thống kiểm thử. Bài viết này sẽ giúp bạn

hình dung một cách rõ ràng, có hệ thống về kiến trúc và vai trò của từng khối

trong UVM Testbench, qua đó hỗ trợ bạn xây dựng môi trường kiểm thử hiệu quả và

chuyên nghiệp.

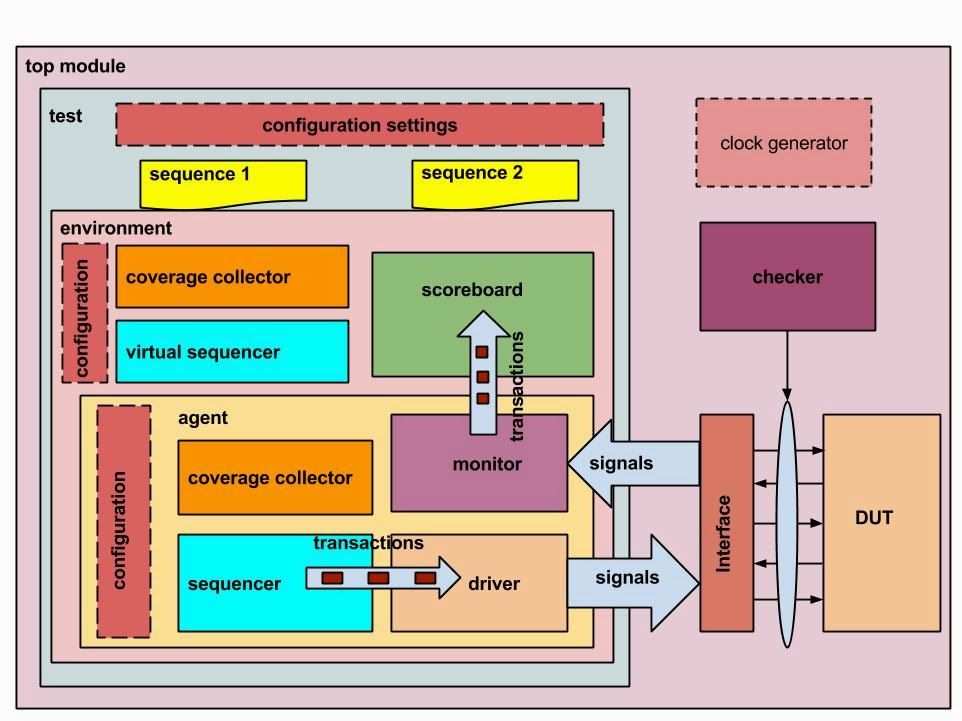

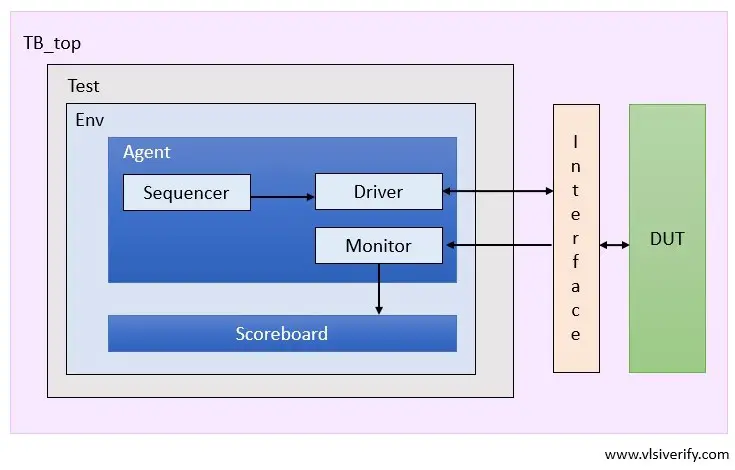

1. UVM

Environment – Môi trường tổng thể điều phối testbench

UVM Environment là lớp bao ngoài cùng, đóng vai trò tổ chức,

cấu hình và kết nối các thành phần như agent, scoreboard, monitor,... Đây chính

là nơi “gắn kết” mọi thành phần trong testbench lại với nhau. Trong môi trường

UVM, bạn có thể tùy chỉnh nhiều loại agent để xử lý các giao thức khác nhau,

giúp hệ thống có khả năng mở rộng cao.

Trong thực tế, khi bạn có một thiết kế với nhiều giao tiếp

(ví dụ như một SoC có SPI, UART, và AXI), UVM environment sẽ là nơi bạn khởi tạo

và cấu hình từng agent tương ứng, rồi kết nối chúng với các khối kiểm tra và

phân tích.

2. UVM

Test – Kịch bản kiểm thử tổng thể

UVM Test là nơi bạn xây dựng và thực thi các bài kiểm thử

cho DUT (Design Under Test). Thành phần này sẽ khởi tạo environment, cấu hình

các thông số hoạt động, và kích hoạt các sequence mong muốn.

Một bài test trong UVM không đơn thuần là "gửi tín hiệu"

đến DUT – nó có thể kiểm thử các chế độ hoạt động, tạo ra hàng loạt tình huống

bất thường, hoặc đo lường các chỉ số hiệu suất của hệ thống. Đây là lý do UVM

Test đóng vai trò như “bài kiểm tra cuối kỳ” với độ tùy biến cao.

3. UVM

Agent – Tác nhân chuyên trách theo từng giao thức

Mỗi agent trong UVM được thiết kế để tương tác với một giao

thức cụ thể như AHB, APB, UART, SPI, v.v. Một agent bao gồm ba thành phần

chính: sequencer, driver và monitor.

Sự phân chia ba thành phần này cho phép agent hoạt động độc

lập và có khả năng tái sử dụng linh hoạt.

4. UVM

Scoreboard – Bộ so sánh kết quả

Scoreboard là nơi đánh giá kết quả thực tế từ DUT so với kết

quả kỳ vọng. Nó là thành phần “phán xét” đúng sai của toàn bộ bài kiểm thử. Các

dữ liệu từ monitor sẽ được gửi về scoreboard để thực hiện việc so sánh.

Trong các thiết kế phức tạp, scoreboard có thể bao gồm nhiều

thuật toán so sánh, từ đơn giản như so sánh từng gói dữ liệu đến phức tạp như

phân tích thứ tự, kiểm tra thời gian phản hồi, hoặc kiểm thử tích hợp nhiều

giao thức.

5.

Interface – Giao diện kết nối với thiết kế

Interface trong UVM là tập hợp các tín hiệu vật lý hoặc

logic kết nối giữa testbench và DUT. Đây là nơi chứa định nghĩa các cổng clock,

reset, tín hiệu điều khiển, dữ liệu vào ra,...

Thông qua interface, các component như driver và monitor có

thể tương tác gián tiếp với DUT. Việc trừu tượng hóa interface giúp việc thiết

kế testbench trở nên gọn gàng, dễ thay đổi và dễ mở rộng hơn.

6.

Synchronization và Configuration – Các yếu tố bổ trợ

Ngoài các thành phần chính kể trên, một testbench UVM hoàn

chỉnh còn đi kèm với các khối hỗ trợ như configuration database (dùng để truyền

thông tin giữa các component), phase system (quản lý thời gian khởi tạo và hoạt

động), và cơ chế đồng bộ hóa giữa các sequence.

Việc nắm vững cách hoạt động của những cơ chế này sẽ giúp bạn

có thể xây dựng các môi trường test phức tạp, hỗ trợ test song song nhiều luồng

dữ liệu hoặc nhiều clock domain.

Tổng kết

Một UVM Testbench được tổ chức khoa học với đầy đủ các thành

phần như environment, agent, driver, monitor, sequencer, scoreboard và test sẽ

mang lại khả năng kiểm thử mạnh mẽ, tái sử dụng cao, và phù hợp với các dự án

công nghiệp hiện đại.

Việc hiểu rõ từng thành phần không chỉ giúp bạn debug dễ

hơn, mà còn là yếu tố bắt buộc nếu bạn muốn phát triển sự nghiệp trong lĩnh vực

Verification Engineer.

Đây không chỉ là kỹ năng viết testbench – mà là khả năng tổ

chức và kiểm soát chất lượng thiết kế vi mạch một cách toàn diện, chuyên nghiệp.

Sat, 19 Jul 2025

Sat, 19 Jul 2025

Sat, 19 Jul 2025

Để lại bình luận