Netlist – 'Bản đồ mạch điện' giúp chip đi từ ý tưởng đến thực tế

Sat, 19 Jul 2025

Theo dõi những câu chuyện của các học giả và các chuyến thám hiểm nghiên cứu của họ

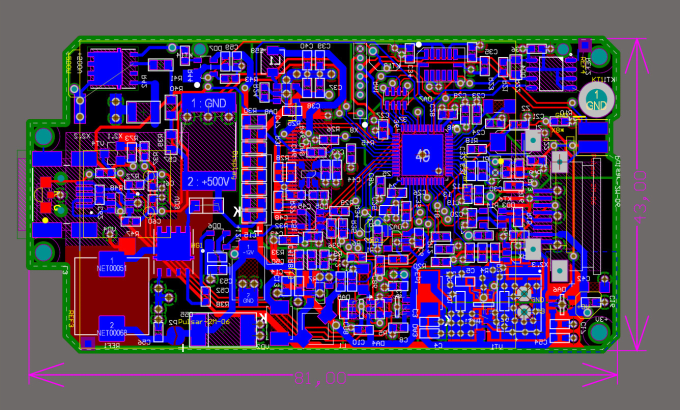

Trong thiết kế vi mạch số hiện đại, kiểm thử (testing) là bước

không thể thiếu để đảm bảo chip hoạt động chính xác sau quá trình chế tạo. Một

hệ thống vi mạch có thể chứa từ vài trăm nghìn đến hàng tỷ phần tử logic –

trong đó riêng các flip-flop đã có thể lên đến hàng triệu đơn vị. Chỉ cần một lỗi

nhỏ cũng có thể dẫn đến sai lệch toàn bộ hành vi hệ thống. Tuy nhiên, việc phát

hiện lỗi ở những phần tử logic “ẩn sâu” bên trong mạch là một bài toán đầy

thách thức, vì ta không thể quan sát trực tiếp chúng như quan sát tín hiệu đầu

vào hay đầu ra.

Để giải quyết vấn đề đó, ngành thiết kế vi mạch đã phát triển

một kỹ thuật mạnh mẽ mang tên Scan Chain – giải pháp giúp "soi lỗi"

tận bên trong lõi logic của con chip, được xem là trụ cột trong lĩnh vực Design-for-Testability

(DFT).

1. Scan

Chain là gì?

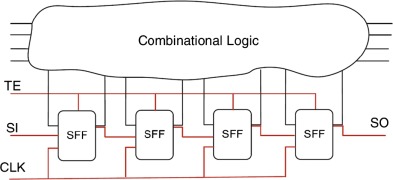

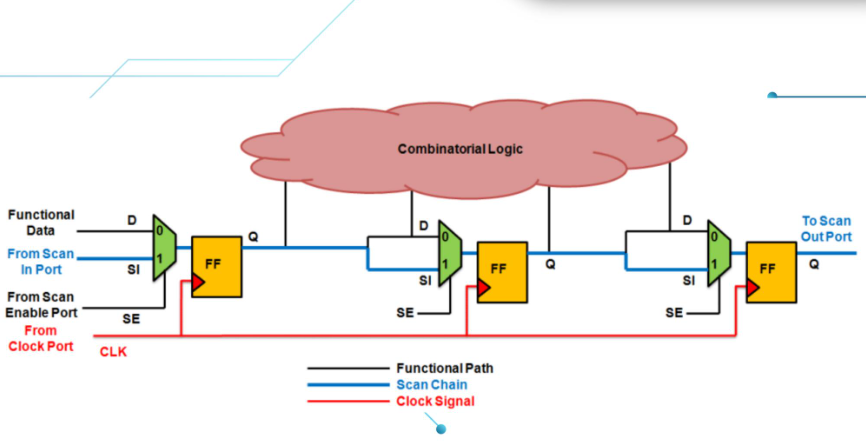

Scan Chain là một kỹ thuật kiểm thử logic được áp dụng

phổ biến trong các vi mạch số, đặc biệt là SoC (System-on-Chip), ASIC hoặc FPGA

quy mô lớn. Ý tưởng chính là: biến tất cả các flip-flop trong mạch thành

một chuỗi liên kết logic (shift register) khi ở chế độ kiểm thử.

Mỗi flip-flop trong mạch được thiết kế để có hai chế độ

hoạt động:

Khi kích hoạt tín hiệu scan_enable, toàn bộ hệ thống

các flip-flop sẽ hoạt động như một dãy logic có thể đọc/ghi dữ liệu từ bên

ngoài chip. Chính cơ chế này cho phép ta đưa dữ liệu vào nội bộ mạch để kiểm

tra hoạt động, và đọc dữ liệu ra để phân tích lỗi.

2. Scan

Chain hoạt động như thế nào?

Quy trình kiểm thử với scan chain bao gồm ba bước cơ bản:

a. Shift In – Nạp dữ liệu kiểm thử

Hệ thống nhận một dãy bit đầu vào (gọi là test vector)

thông qua cổng Scan Input. Các bit này được “shift” tuần tự vào từng flip-flop

thông qua chuỗi scan chain. Mỗi flip-flop lưu trữ một bit dữ liệu, giống như từng

mắt xích trong một sợi dây logic.

b. Capture – Bắt dữ liệu phản hồi

Sau khi đã nạp xong vector, scan_enable được tắt, mạch hoạt

động trở lại bình thường. Dữ liệu được lan truyền qua khối logic tổ hợp. Giá trị

đầu ra của các flip-flop ở bước này sẽ phản ánh phản ứng của mạch trước dữ liệu

đầu vào kiểm thử.

c. Shift Out – Đọc dữ liệu đầu ra

Sau quá trình hoạt động, các flip-flop sẽ chứa phản hồi của

hệ thống. Ta kích hoạt lại scan_enable để shift toàn bộ dữ liệu đầu ra từ bên

trong mạch ra cổng Scan Output. Sau đó, các giá trị này được phân tích và so

sánh với giá trị mong đợi để phát hiện lỗi.

Các công cụ ATPG (Automatic Test Pattern Generation)

sẽ tự động sinh ra hàng loạt test vector tối ưu, giúp phát hiện và định vị lỗi

một cách nhanh chóng – kể cả những lỗi xảy ra sâu bên trong logic.

3. Lợi

ích của kỹ thuật Scan Chain

Việc tích hợp scan chain trong thiết kế mạch số mang lại nhiều

lợi ích quan trọng:

4. Học

Scan Chain – Khởi đầu cho kỹ sư DFT chuyên nghiệp

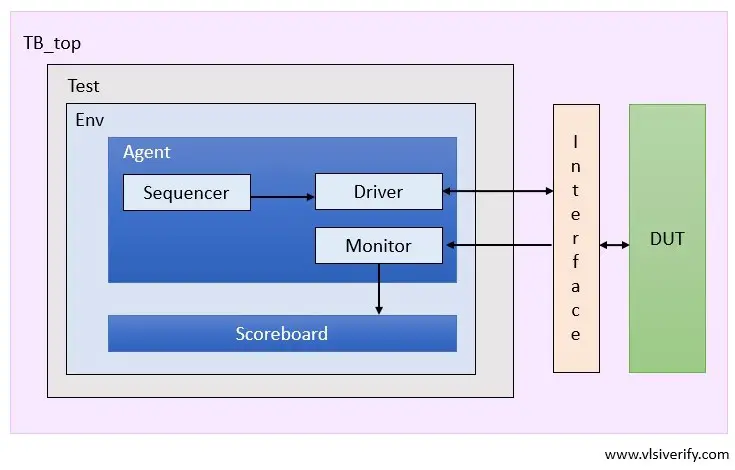

Scan chain là kiến thức nền tảng trong lĩnh vực Design-for-Testability

và là bước đầu tiên để trở thành kỹ sư kiểm thử vi mạch (DFT Engineer). Một lộ

trình học hiệu quả sẽ bao gồm:

Kết luận

Scan Chain không đơn thuần là một kỹ thuật phụ trợ – nó là

công cụ cốt lõi giúp hiểu được trạng thái bên trong vi mạch, một nhiệm vụ

gần như không thể thực hiện bằng bất kỳ phương pháp quan sát trực tiếp nào. Nếu

xem flip-flop là các tế bào của mạch số, thì scan chain chính là “dòng máu” nối

chúng lại – để kiểm thử, để phân tích và để đảm bảo hệ thống hoạt động ổn định

từ khi vừa bước ra khỏi dây chuyền sản xuất.

Sat, 19 Jul 2025

Sat, 19 Jul 2025

Sat, 19 Jul 2025

Để lại bình luận